- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383876 > T8536A (Lineage Power) Quad Programmable Codec Chip Set(四通道可編程編解碼器芯片組) PDF資料下載

參數(shù)資料

| 型號: | T8536A |

| 廠商: | Lineage Power |

| 元件分類: | Codec |

| 英文描述: | Quad Programmable Codec Chip Set(四通道可編程編解碼器芯片組) |

| 中文描述: | 四可編程芯片集編解碼器(四通道可編程編解碼器芯片組) |

| 文件頁數(shù): | 2/2頁 |

| 文件大?。?/td> | 140K |

| 代理商: | T8536A |

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No

rights under any patent accompany the sale of any such product(s) or information.

Copyright 2000 Lucent Technologies Inc.

All Rights Reserved

Printed in U.S.A.

June 2000

PB00-058ALC

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET:

http://www.lucent.com/micro

E-MAIL:

docmaster@micro.lucent.com

N. AMERICA:

Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447

, FAX 610-712-4106 (In CANADA:

1-800-553-2448

, FAX 610-712-4106)

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833

, FAX (65) 777 7495

CHINA:

Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai

200233 P. R. China

Tel. (86) 21 6440 0468

,

ext. 325

, FAX (86) 21 6440 0652

JAPAN:

Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600

, FAX (81) 3 5421 1700

EUROPE:

Data Requests: MICROELECTRONICS GROUP DATALINE:

Tel. (44) 7000 582 368

, FAX (44) 1189 328 148

Technical Inquiries: GERMANY:

(49) 89 95086 0

(Munich), UNITED KINGDOM:

(44) 1344 865 900

(Ascot),

FRANCE:

(33) 1 40 83 68 00

(Paris), SWEDEN:

(46) 8 594 607 00

(Stockholm), FINLAND:

(358) 9 4354 2800

(Helsinki),

ITALY:

(39) 02 6608131

(Milan), SPAIN:

(34) 1 807 1441

(Madrid)

Product Brief

June 2000

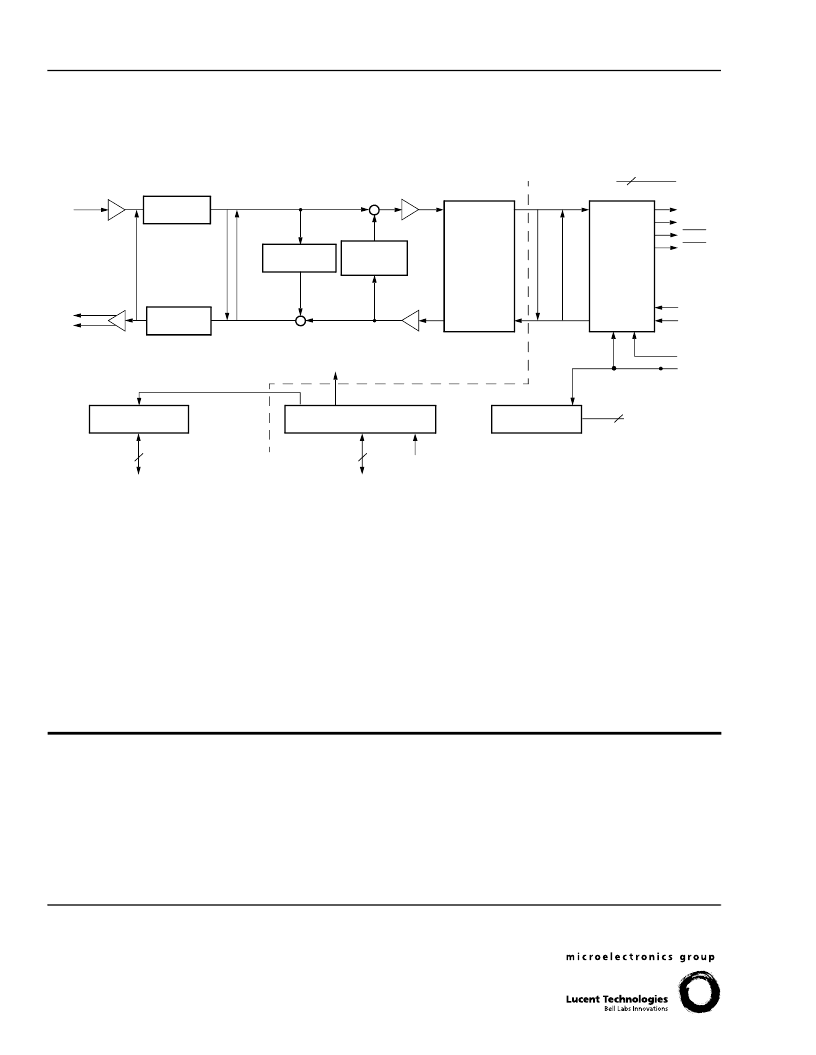

T8535A/T8536A Quad Programmable Codec

Functional Block Diagram

.

5-8125aF

* Second PCM port not available in all package types.

RST

SLIC

TO/FROM

ANALOG

GAIN

A/D

CONVERTER

ANALOG

BUFFER

D/A

CONVERTER

D

L

A

L

D

L

TERMINATION

IMPEDANCE

HYBRID

BALANCE

NETWORK

DIGITAL GAIN

(GAIN TRANSFER)

μ

-LAW

OR

A-LAW

PER

CHANNEL

COMMON

A

L

D

L

PCM BUS

INTERFACE

DX0

DX1*

TSX0*

TSX1*

DR1*

TO/FROM

PCM BUS

POWER AND

GROUND

18

FS

BCLK

SLIC

CONTROL LATCHES

MICROPROCESSOR CONTROL

CONTROL AND DATA SIGNALS

4

SERIAL

CONTROL

INTERFACE

PER

CHANNEL

COMMON

0 TO 6

FREQUENCY

SYNTHESIZER

0 TO 3

FILTER

CONVERSION

DIGITAL GAIN

(GAIN TRANSFER)

DR0

VF

R

OPn

VF

R

ONn

VF

X

In

相關PDF資料 |

PDF描述 |

|---|---|

| T8536 | Quad Programmable Codec(四通道可編程編解碼器) |

| T8535 | Quad Programmable Codec(四通道可編程編解碼器) |

| T8538A | Quad Programmable Codec(四通道可編程編解碼器) |

| T85HF10 | POWER RECTIFIER DIODES |

| T85HF100 | POWER RECTIFIER DIODES |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| T8536B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8535B/T8536B Quad Programmable Codec |

| T8538B | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8538B Quad Programmable Codec |

| T85471G | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T85471J | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T8550VBAAA | 制造商:Arcolectric 功能描述:2 Pole Miniature rocker switch(Curved) 制造商:Arcolectric 功能描述:Double Pole,Miniature rocker switch(Curved),Standard Body with Terminal Barrier |

發(fā)布緊急采購,3分鐘左右您將得到回復。