- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1969 > ST16C450CP40-F (Exar Corporation)IC INTERFACE UART PDF資料下載

參數(shù)資料

| 型號: | ST16C450CP40-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 7/28頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC INTERFACE UART |

| 標準包裝: | 9 |

| 系列: | * |

| 其它名稱: | 1016-1760 |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

ST16C450

15

Rev. 4.20

LCR BIT-5 = logic 0, parity is not forced (normal default

condition)

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 0, parity bit

is forced to a logical 1 for the transmit and receive

data.

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 1, parity bit

is forced to a logical 0 for the transmit and receive

data.

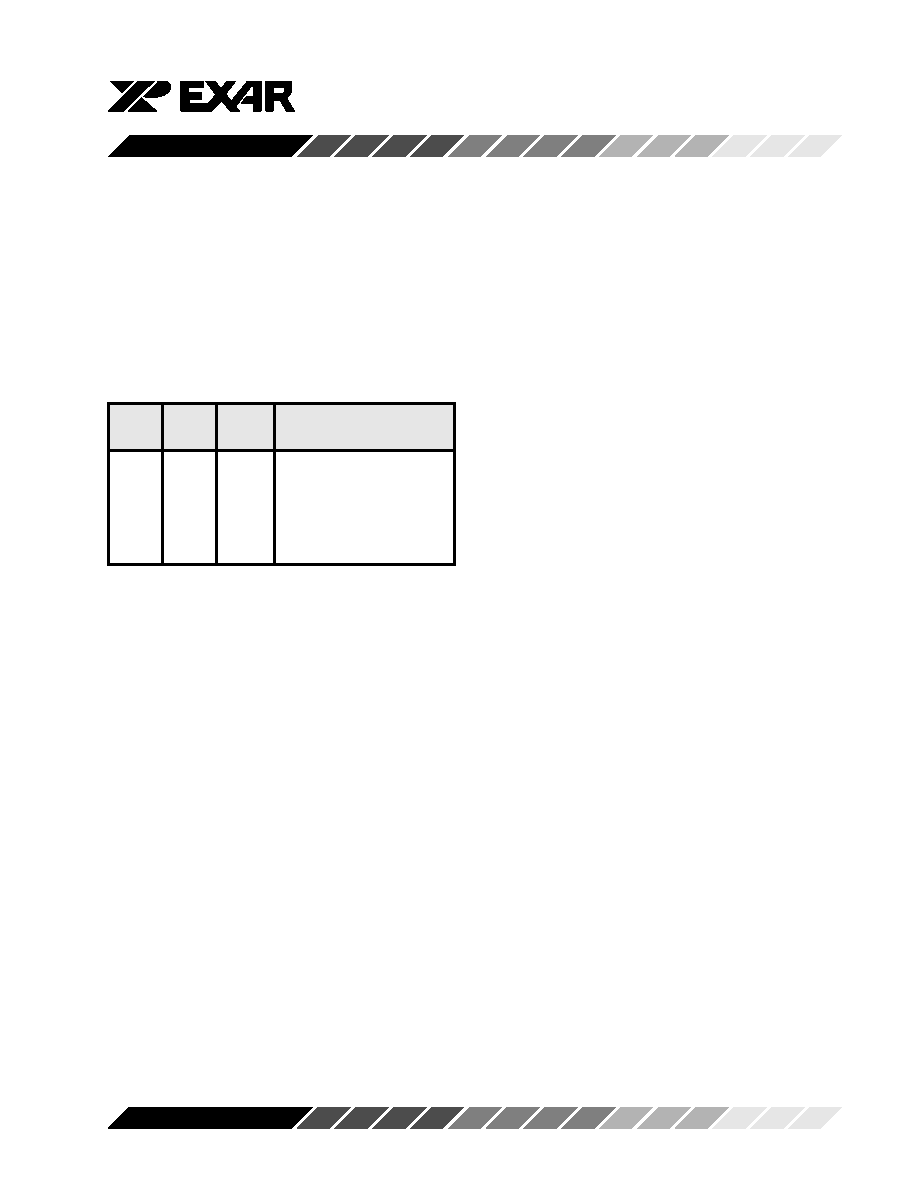

LCR

Parity selection

Bit-5

Bit-4

Bit-3

X

0

No parity

0

1

Odd parity

0

1

Even parity

1

0

1

Force parity”1”

1

Forced parity “0”

LCR BIT-6:

When enabled the Break control bit causes a break

condition to be transmitted (the TX output is forced to

a logic 0 state). This condition exists until disabled by

setting LCR bit-6 to a logic 0.

Logic 0 = No TX break condition. (normal default

condition)

Logic 1 = Forces the transmitter output (TX) to a logic

0 for alerting the remote receiver to a line break

condition.

LCR BIT-7:

The internal baud rate counter latch and Enhance

Feature mode enable.

Logic 0 = Divisor latch disabled. (normal default

condition)

Logic 1 = Divisor latch and enhanced feature register

enabled.

Modem Control Register (MCR)

This register controls the interface with the modem or a

peripheral device.

MCR BIT-0:

Logic 0 = Force -DTR output to a logic 1. (normal

default condition)

Logic 1 = Force -DTR output to a logic 0.

MCR BIT-1:

Logic 0 = Force -RTS output to a logic 1. (normal default

condition)

Logic 1 = Force -RTS output to a logic 0.

MCR BIT-2:

Logic 0 = Set -OP1 output to a logic 1. (normal default

condition)

Logic 1 = Set -OP1 output to a logic 0.

MCR BIT-3:

Logic 0 = Set -OP2 output to a logic 1. (normal default

condition)

Logic 1 = Set -OP2 output to a logic 0.

MCR BIT-4:

Logic 0 = Disable loop-back mode. (normal default

condition)

Logic 1 = Enable local loop-back mode (diagnostics).

MCR BIT 5-7: Not used and set to “0”.

Line Status Register (LSR)

This register provides the status of data transfers

between. the ST16C450 and the CPU.

LSR BIT-0:

Logic 0 = No data in receive holding register. (normal

default condition)

Logic 1 = Data has been received and is saved in the

receive holding register.

LSR BIT-1:

Logic 0 = No overrun error. (normal default condition)

Logic 1 = Overrun error. A data overrun error occurred

in the receive shift register. This happens when addi-

tional data arrives while the RHR is full. In this case the

previous data in the shift register is overwritten. Note

that under this condition the data byte in the receive

shift register is not transfer into the RHR, therefore the

data in the RHR is not corrupted by the error.

LSR BIT-2:

Logic 0 = No parity error (normal default condition)

Logic 1 = Parity error. The receive character does not

have correct parity information and is suspect.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST16C452IJ68-F | IC UART W/PAR PORT DUAL 68PLCC |

| ST16C454IJ68TR-F | IC UART QUAD 68PLCC |

| ST16C550CJ44-F | IC UART FIFO 16B SGL 44PLCC |

| ST16C550CP40-F | IC INTERFACE UART |

| ST16C552IJ68TR-F | IC UART FIFO 16B DUAL 68PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST16C450CQ48 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

| ST16C450CQ48-F | 功能描述:UART 接口集成電路 SINGLE UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| ST16C450CQ48TR-F | 功能描述:UART 接口集成電路 SINGLE UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| ST16C450IJ44 | 制造商:EXAR 制造商全稱:EXAR 功能描述:UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART) |

| ST16C450IJ44-F | 功能描述:UART 接口集成電路 SINGLE UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。