- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98141 > SPL505YC264ATT PROC SPECIFIC CLOCK GENERATOR, PDSO64 PDF資料下載

參數(shù)資料

| 型號(hào): | SPL505YC264ATT |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| 封裝: | 6 X 17 MM, LEAD FREE, MO-153, TSSOP-64 |

| 文件頁(yè)數(shù): | 3/27頁(yè) |

| 文件大?。?/td> | 314K |

| 代理商: | SPL505YC264ATT |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

SPL505YC264BT

Rev 1.4 May 21, 2007

Page 11 of 27

3

0

CPU2_AMT_EN

2

1

CPU1_AMT_EN

1

HW

PCI-E_GEN2

PCI-E_Gen2 Compliant

0 = non Gen2, 1= Gen2 Compliant

0

1

CPU2_STP_CRTL

Allow control of CPU2 with assertion of CPU_STOP#

0 = Free running, 1 = Stopped with CPU_STOP#

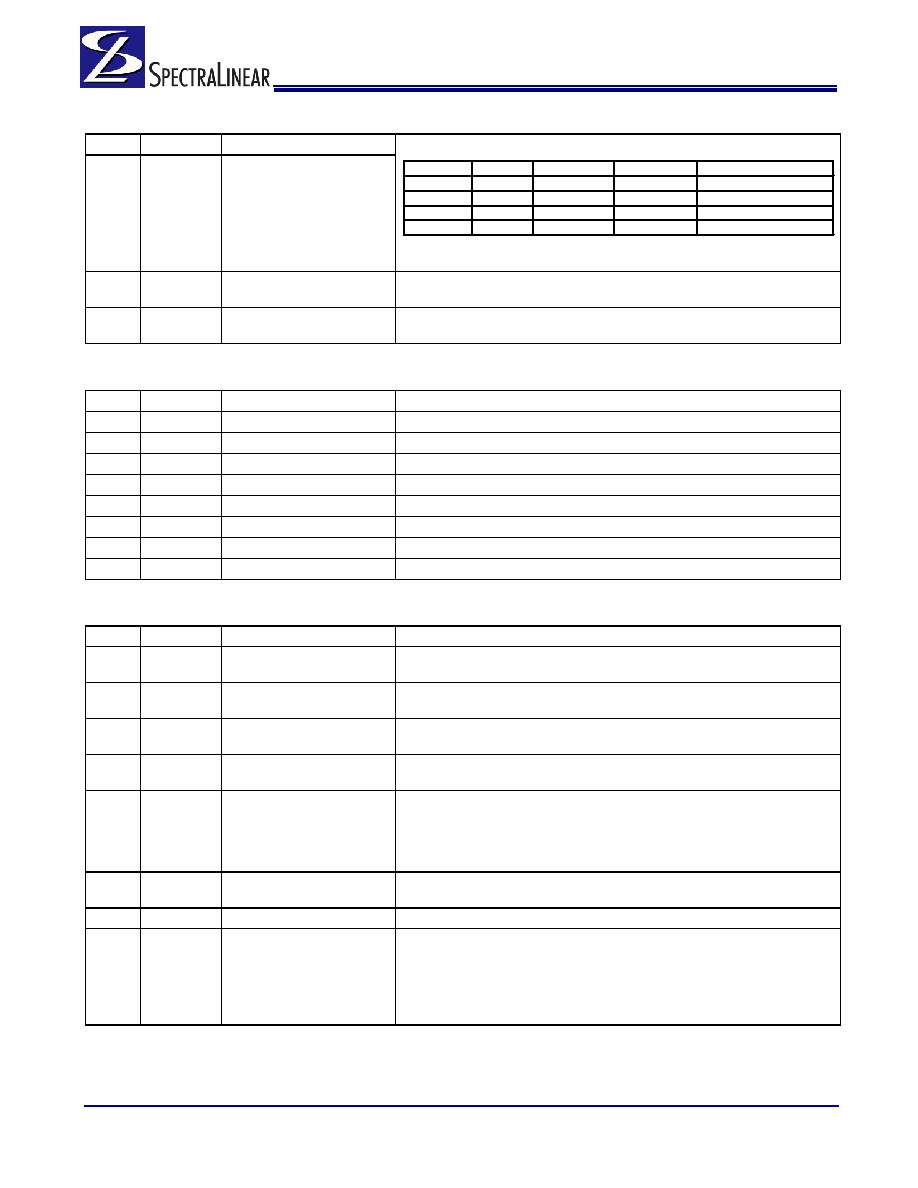

Byte 11 Control Register 11

PCIF0/ITP_EN

AMT_EN

CPU2_AMT_EN

CPU1_AMT_EN

Description

x

1

0

Reserved

x

1

0

1

CPU1 = M1 Clock

1

0

CPU2 - M1 Clock

1

CPU1 and CPU2 = M1 Clock

Byte 12 Byte Count

Bit

@Pup

Name

Description

7

0

RESERVED

6

0

RESERVED

5

0

BC5

Byte count

4

0

BC4

Byte count

3

1

BC3

Byte count

2

1

BC2

Byte count

1

0

BC1

Byte count

0

1

BC0

Byte count

Byte 13 Control Register 13

Bit

@Pup

Name

Description

7

1

USB_DSC1

USB drive strength control, See Byte 18 for more setting

0 = Low, 1= High

6

1

PCI/PCIF_DSC1

PCI drive strength control, See Byte 18 for more setting

0 = Low, 1 = High

5

0

PLL1_Spread

Select percentage of spread for PLL1

0 = 0.5%, 1=1%

4

0

SATA_SS_EN

Enable SATA spread modulation,

0 = Spread Disabled 1 = Spread Enabled

3

1

EN_CFG0_SET

By defalult CFG0 pin strap sets the SMBus initial values to select the HW

mode. When this bit is written0, subsequent SMBus accesses is the Lathes

Open state, can overwrite the CFG0 pin setting into the SMBus bits and set

the mode before the M0 state: specifically B0b2, B1b[6,4,3], B9b1, B11b5

2

1

SE1/SE2_DSC1

SE1 and SE2 drive strength control, See Byte 18 for more setting

0 = Low, 1 = High

1

RESERVED

0

1

SW_PCI

SW PCI_STP# Function

0 = SW PCI_STP assert, 1 = SW PCI_STP deassert

When this bit is set to 0, all STOPPABLE PCI, PCIF and SRC outputs will

be stopped in a synchronous manner with no short pulses.

When this bit is set to 1, all STOPPED PCI, PCIF and SRC outputs will

resume in a synchronous manner with no short pulses.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SPL505YC264BT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| SPL505YC264BT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| SPW08F0D | SINGLE COLOR LED, PURE WHITE, 3.5 mm |

| SSC-SFT825N-S | TRIPLE COLOR LED, RED/GREEN/BLUE, 2.4 mm |

| SSI32C452-CP | 20 Mbps, ST506; ST412; ST412HP; SA100 COMPATIBLE, FIXED DISK CONTROLLER, PDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SPL505YC264BT | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 CK505 v0.85 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| SPL505YC264BTT | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 CK505 v0.85 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| SPL5100PT | 制造商:CHENMKO 制造商全稱:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER RECTIFIER |

| SPL520LLPT | 制造商:CHENMKO 制造商全稱:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER RECTIFIER |

| SPL53-1024 | 制造商:Power-One 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。