- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98114 > SN74HC646NT (TEXAS INSTRUMENTS INC) HC/UH SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDIP24 PDF資料下載

參數(shù)資料

| 型號: | SN74HC646NT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | HC/UH SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDIP24 |

| 封裝: | ROHS COMPLIANT, PLASTIC, DIP-24 |

| 文件頁數(shù): | 15/15頁 |

| 文件大?。?/td> | 459K |

| 代理商: | SN74HC646NT |

SN54HC646, SN74HC646

OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCLS150C – DECEMBER 1982 – REVISED MARCH 2003

9

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

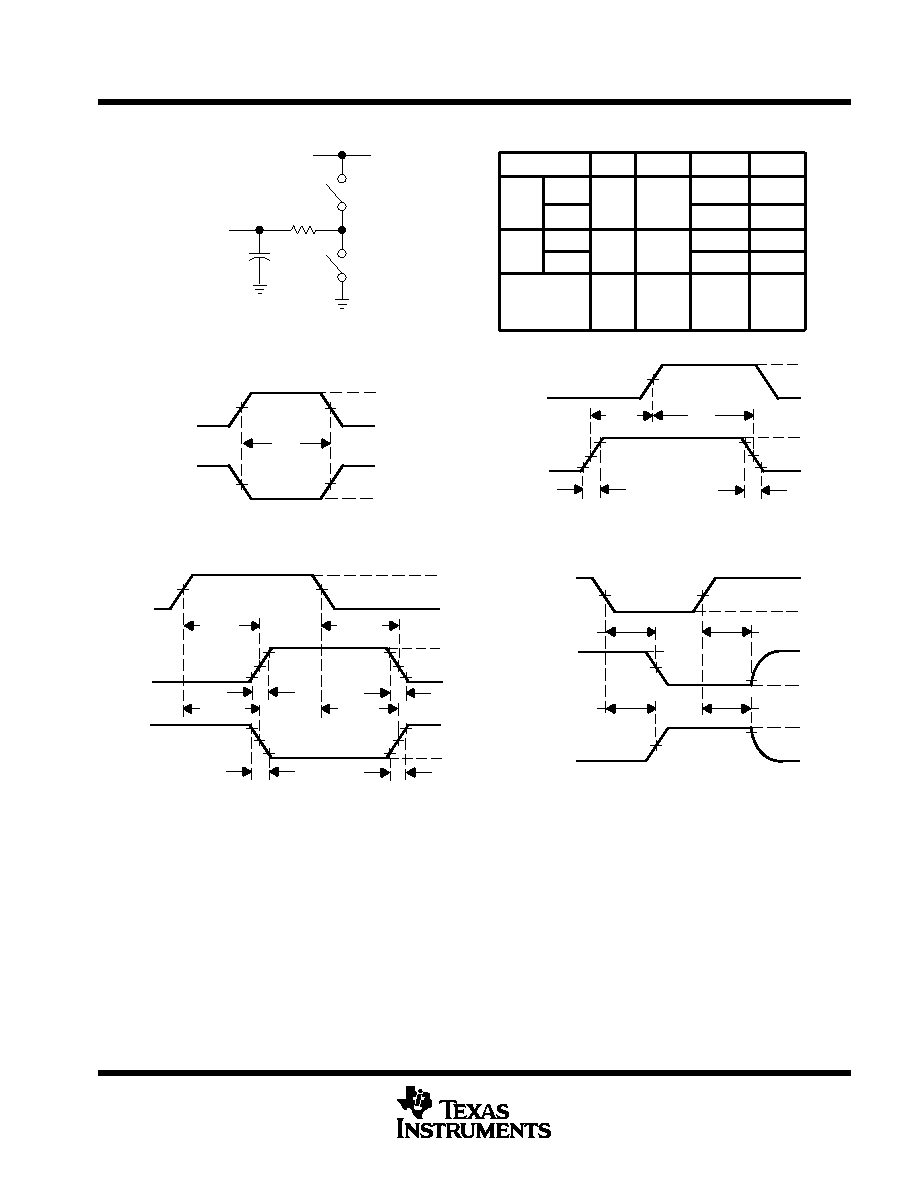

PARAMETER MEASUREMENT INFORMATION

VOLTAGE WAVEFORMS

SETUP AND HOLD AND INPUT RISE AND FALL TIMES

VOLTAGE WAVEFORMS

PULSE DURATIONS

th

tsu

50%

10%

90%

VCC

0 V

tr

tf

Reference

Input

Data

Input

50%

High-Level

Pulse

50%

VCC

0 V

50%

VCC

0 V

tw

Low-Level

Pulse

VOLTAGE WAVEFORMS

PROPAGATION DELAY AND OUTPUT TRANSITION TIMES

50%

10%

90%

VCC

VOH

VOL

0 V

tr

tf

Input

In-Phase

Output

50%

tPLH

tPHL

50%

10%

90%

VOH

VOL

tr

tf

tPHL

tPLH

Out-of-

Phase

Output

50%

10%

90%

VCC

≈VCC

VOL

0 V

Output

Control

(Low-Level

Enabling)

Output

Waveform 1

(See Note B)

50%

tPZL

tPLZ

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES FOR 3-STATE OUTPUTS

VOH

≈0 V

50%

tPZH

tPHZ

Output

Waveform 2

(See Note B)

≈VCC

Test

Point

From Output

Under Test

RL

VCC

S1

S2

LOAD CIRCUIT

PARAMETER

CL

tPZH

tpd or tt

tdis

ten

tPZL

tPHZ

tPLZ

1 k

1 k

50 pF

or

150 pF

50 pF

Open

Closed

RL

S1

Closed

Open

S2

Open

Closed

Open

50 pF

or

150 pF

Open

––

NOTES: A. CL includes probe and test-fixture capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following

characteristics: PRR

≤ 1 MHz, ZO = 50 , tr = 6 ns, tf = 6 ns.

D. For clock inputs, fmax is measured when the input duty cycle is 50%.

E. The outputs are measured one at a time with one input transition per measurement.

F. tPLZ and tPHZ are the same as tdis.

G. tPZL and tPZH are the same as ten.

H. tPLH and tPHL are the same as tpd.

CL

(see Note A)

Figure 2. Load Circuit and Voltage Waveforms

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74HC684DWRE4 | HC/UH SERIES, 8-BIT MAGNITUDE COMPARATOR, INVERTED OUTPUT, PDSO20 |

| SNJ54HC684WR | HC/UH SERIES, 8-BIT MAGNITUDE COMPARATOR, INVERTED OUTPUT, CDFP20 |

| SN74HC688N | HC/UH SERIES, 8-BIT IDENTITY COMPARATOR, INVERTED OUTPUT, PDIP20 |

| SN74HC688PWRG4 | HC/UH SERIES, 8-BIT IDENTITY COMPARATOR, INVERTED OUTPUT, PDSO20 |

| SN74HC688PWTG4 | HC/UH SERIES, 8-BIT IDENTITY COMPARATOR, INVERTED OUTPUT, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74HC646NTE4 | 功能描述:總線收發(fā)器 Octal Bus Trncvr/Reg W/3-State Otpt RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74HC652DW | 功能描述:總線收發(fā)器 Tri-State Octal Bus RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74HC652DWE4 | 功能描述:總線收發(fā)器 Octal Bus Trncvr/Reg W/3-State Otpt RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74HC652DWG4 | 功能描述:總線收發(fā)器 Octal Bus Transceivr And Registers RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74HC652DWR | 功能描述:總線收發(fā)器 Octal Bus Trncvr/Reg W/3-State Otpt RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。