- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98084 > SM320C6416DGADW60 (TEXAS INSTRUMENTS INC) 64-BIT, 75 MHz, OTHER DSP, CPGA570 PDF資料下載

參數(shù)資料

| 型號: | SM320C6416DGADW60 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 64-BIT, 75 MHz, OTHER DSP, CPGA570 |

| 封裝: | 33 X 33 MM, CERAMIC, FCPGA-570 |

| 文件頁數(shù): | 127/134頁 |

| 文件大小: | 1997K |

| 代理商: | SM320C6416DGADW60 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁當前第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁

SMJ320C6414, SMJ320C6415, SMJ320C6416

FIXEDPOINT DIGITAL SIGNAL PROCESSORS

SGUS050A JANUARY 2004 REVISED MARCH 2004

92

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

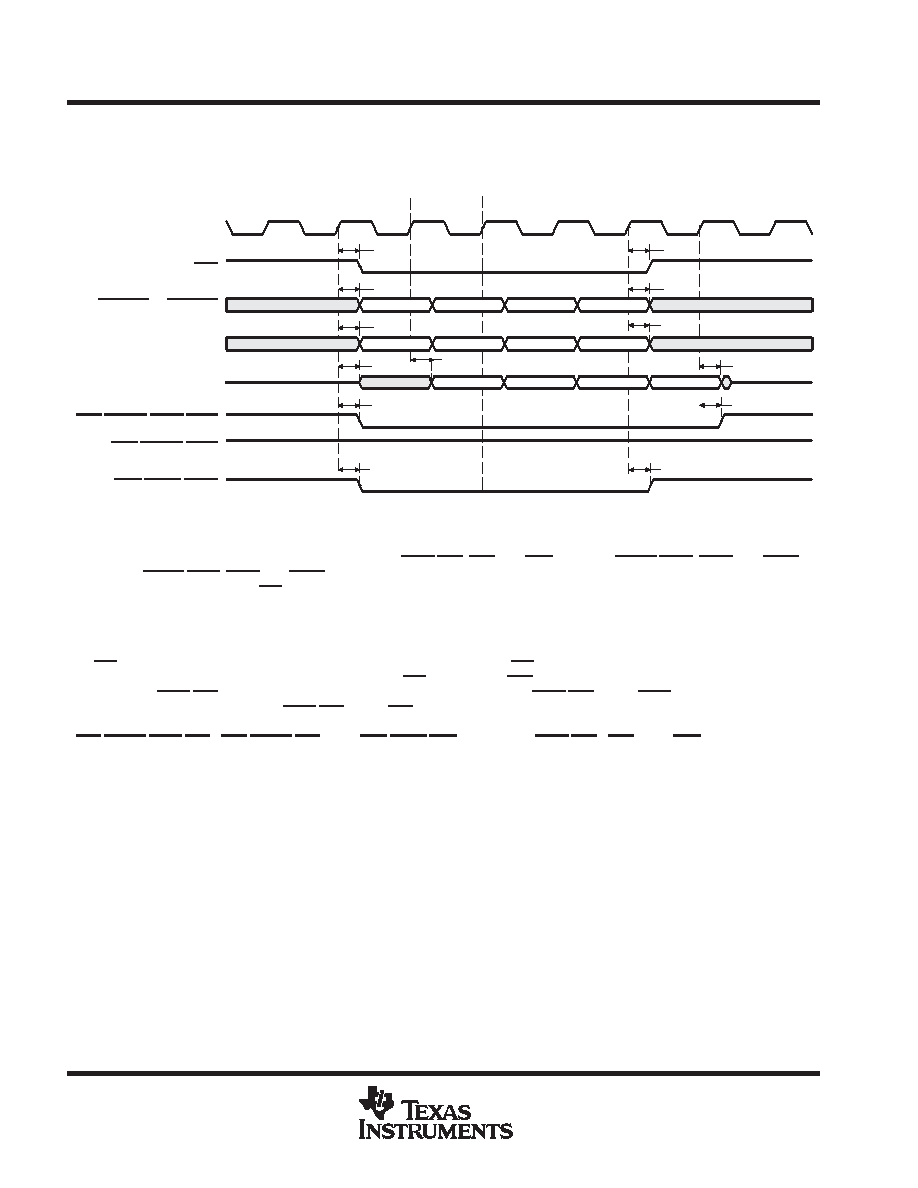

PROGRAMMABLE SYNCHRONOUS INTERFACE TIMING (CONTINUED)

ECLKOUTx

CEx

ABE[7:0] or BBE[1:0]

AEA[22:3] or BEA[20:1]

AED[63:0] or BED[15:0]

ARE/SDCAS/SADS/SRE

AOE/SDRAS/SOE

AWE/SDWE/SWE

BE1

BE2

BE3

BE4

Q1

Q2

Q3

11

3

12

10

4

2

1

8

5

8

EA1

EA2

EA3

EA4

10

Write

Latency =

1

Q4

12

These C64x devices have two EMIFs (EMIFA and EMIFB). All EMIFA signals are prefixed by an “A” and all EMIFB signals are prefixed by a

“B”. Throughout the rest of this document, in generic EMIF areas of discussion, the prefix “A” or “B” may be omitted [e.g., the programmable

synchronous interface access signals are shown as generic (SADS/SRE, SOE, and SWE) instead of ASADS/ASRE, ASOE, and ASWE (for

EMIFA) and BSADS/BSRE, BSOE, and BSWE (for EMIFB)].

The write latency and the length of CEx assertion are programmable via the SYNCWL and CEEXT fields, respectively, in the EMIFx CE Space

Secondary Control register (CExSEC). In this figure, SYNCWL = 1 and CEEXT = 0.

§ The following parameters are programmable via the EMIF CE Space Secondary Control register (CExSEC):

Read latency (SYNCRL): 0-, 1-, 2-, or 3-cycle read latency

Write latency (SYNCWL): 0-, 1-, 2-, or 3-cycle write latency

CEx assertion length (CEEXT): For standard SBSRAM or ZBT SRAM interface, CEx goes inactive after the final command has been issued

(CEEXT = 0). For synchronous FIFO interface with glue, CEx is active when SOE is active (CEEXT = 1).

Function of SADS/SRE (RENEN): For standard SBSRAM or ZBT SRAM interface, SADS/SRE acts as SADS with deselect cycles

(RENEN = 0). For FIFO interface, SADS/SRE acts as SRE with NO deselect cycles (RENEN = 1).

Synchronization clock (SNCCLK): Synchronized to ECLKOUT1 or ECLKOUT2

ARE/SDCAS/SADS/SRE, AOE/SDRAS/SOE, and AWE/SDWE/SWE operate as SADS/SRE, SOE, and SWE, respectively, during

programmable synchronous interface accesses.

Figure 26. Programmable Synchronous Interface Write Timing for EMIFA and EMIFB

(With Write Latency = 1)§

相關PDF資料 |

PDF描述 |

|---|---|

| SMJ320C6701GLPW16 | 32-BIT, 166.66 MHz, OTHER DSP, CBGA429 |

| SMJ34010-50FDM | GRAPHICS PROCESSOR, CQCC68 |

| SMJ34010-40GBM | GRAPHICS PROCESSOR, CPGA68 |

| SMJ34010FDM | GRAPHICS PROCESSOR, CQCC68 |

| SMJ9914AFDS | IEEE 488 (GPIB) BUS CONTROLLER, CQCC44 |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SM320C6424GDUQ6EP | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC EP Fixed-Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| SM320C6455BGTZEP | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Enh Product Fixed- Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| SM320C6455BGTZSEP | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Enh Product Fixed- Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| SM320C6455-EP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6472EGTZA6 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Fixed-Pt Dig Sig Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復。