- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374788 > SI5364-F-BC (Electronic Theatre Controls, Inc.) SONET/SDH PRECISION PORT CARD CLOCK IC PDF資料下載

參數(shù)資料

| 型號(hào): | SI5364-F-BC |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | SONET/SDH PRECISION PORT CARD CLOCK IC |

| 中文描述: | SONET / SDH的精密端口卡時(shí)鐘IC |

| 文件頁(yè)數(shù): | 30/40頁(yè) |

| 文件大小: | 565K |

| 代理商: | SI5364-F-BC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

Si5364

30

Rev. 2.2

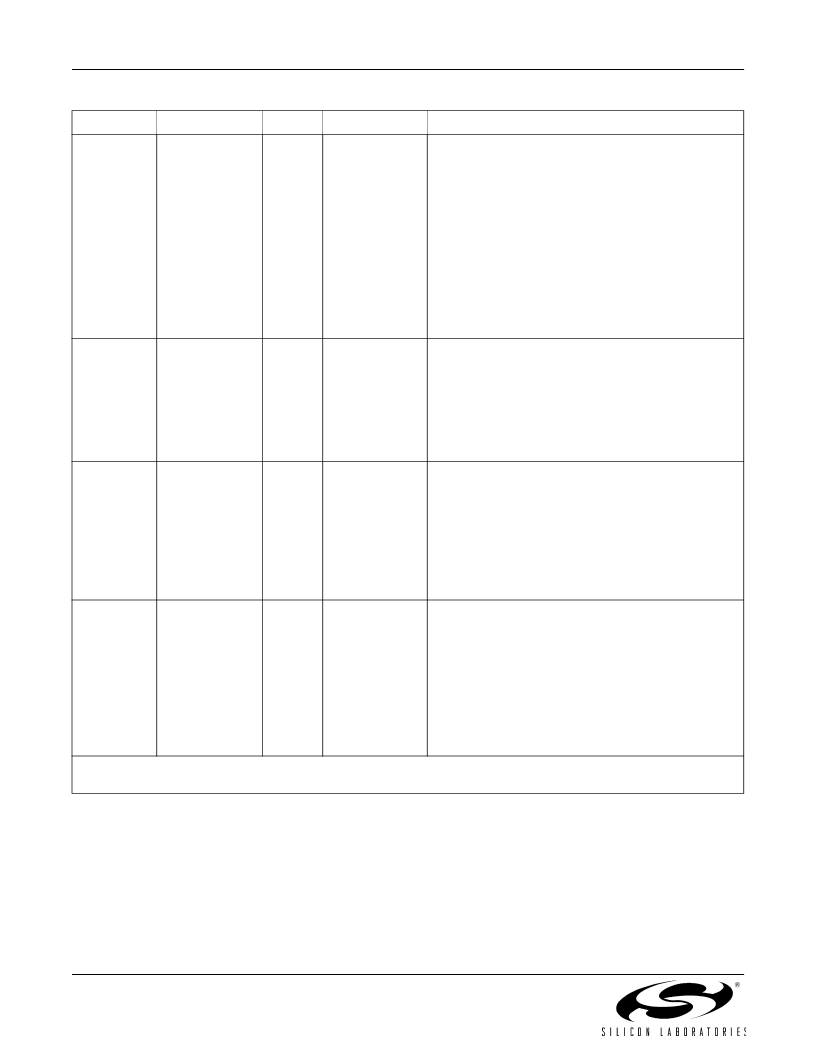

A9

F_ACTV

O

LVTTL

REF/CLKIN_F is Active.

Active high output indicates that REF/CLKIN_F is

selected as the clock input to the DSPLL.

The DH_ACTV output takes precedence over this

signal as an indicator of the DSPLL clock input sta-

tus. When this output is high and the DH_ACTV out-

put is low, REF/CLKIN_F is being used by the

DSPLL to generate the SONET/SDH compatible out-

put clocks. When this output is high and the

DH_ACTV output is high, REF/CLKIN_F is selected,

but the DSPLL is in digital hold mode. Refer to

DH_ACTV.

A10

DH_ACTV

O

LVTTL

Digital Hold Mode Active.

Active high output indicates that the DSPLL is in

digital hold mode. Digital hold mode locks the current

state of the DSPLL and forces the DSPLL to

continue generation of the output clocks with no

additional phase or frequency information from the

input clocks.

C10

RVRT

I*

LVTTL

Revertive Switching.

Selects the revertive switching mode during auto-

matic switching operation. If this input is high during

automatic switching, the revertive switching mode is

selected. The highest priority reference source that is

valid is selected as the DSPLL reference source.

See AUTOSEL pin description. During manual mode

of operation, this input has no effect.

K2

RSTN/CAL

I*

LVTTL

Reset/Calibrate.

When low, all outputs are forced into a high-imped-

ance state, the DSPLL is forced out-of-lock, and the

device control logic is reset.

A low-to-high transition on RSTN/CAL initializes all

digital logic to a known condition, enables the device

outputs, and initiates self-calibration of the DSPLL.

At the completion of self-calibration, the DSPLL

begins to lock to the selected clock input signal.

Table 10. Pin Descriptions (Continued)

I/O

Signal Level

Pin #

Pin Name

Description

*Note:

The LVTTL inputs on the Si5364 device have an internal pulldown mechanism that causes the input to default to a logic

low state if the input is not driven from an external source.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SI5600 | SiPHY-TM OC-192/STM-64 SONET/SDH TRANSCEIVER |

| SI5600-BC | SiPHY-TM OC-192/STM-64 SONET/SDH TRANSCEIVER |

| SI7661 | HEATSINK TO-202 CLIP-ON .58 BK |

| SI7661DJ | HEATSINK TO-220 CLIP-ON BLK |

| SI7661CJ | CMOS Voltage Converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI5364-G-BC | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 SONET/SDH Precision Port Card 19 155 622 RoHS:否 制造商:Silicon Labs 類(lèi)型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| Si5364-H-BL | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 SONET/SDH Prcsn Port Card Clock Multiplr RoHS:否 制造商:Silicon Labs 類(lèi)型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| Si5364-H-BLR | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 SONET/SDH Precision 19MHz 155MHz 622MHz RoHS:否 制造商:Silicon Labs 類(lèi)型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| Si5364-H-GL | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 SONET/SDH Prcsn Port Card Clock Multiplr RoHS:否 制造商:Silicon Labs 類(lèi)型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| Si5364-H-GLR | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 SONET/SDH Precision 19MHz 155MHz 622MHz RoHS:否 制造商:Silicon Labs 類(lèi)型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。