- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385820 > SCN68661 (NXP Semiconductors N.V.) Enhanced programmable communications interface EPCI PDF資料下載

參數(shù)資料

| 型號: | SCN68661 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Enhanced programmable communications interface EPCI |

| 中文描述: | 增強(qiáng)的可編程通信接口到ePCI |

| 文件頁數(shù): | 11/19頁 |

| 文件大小: | 131K |

| 代理商: | SCN68661 |

Philips Semiconductors

Product specification

SCN2661/SCN68661

Enhanced programmable communications

interface (EPCI)

1994 Apr 27

11

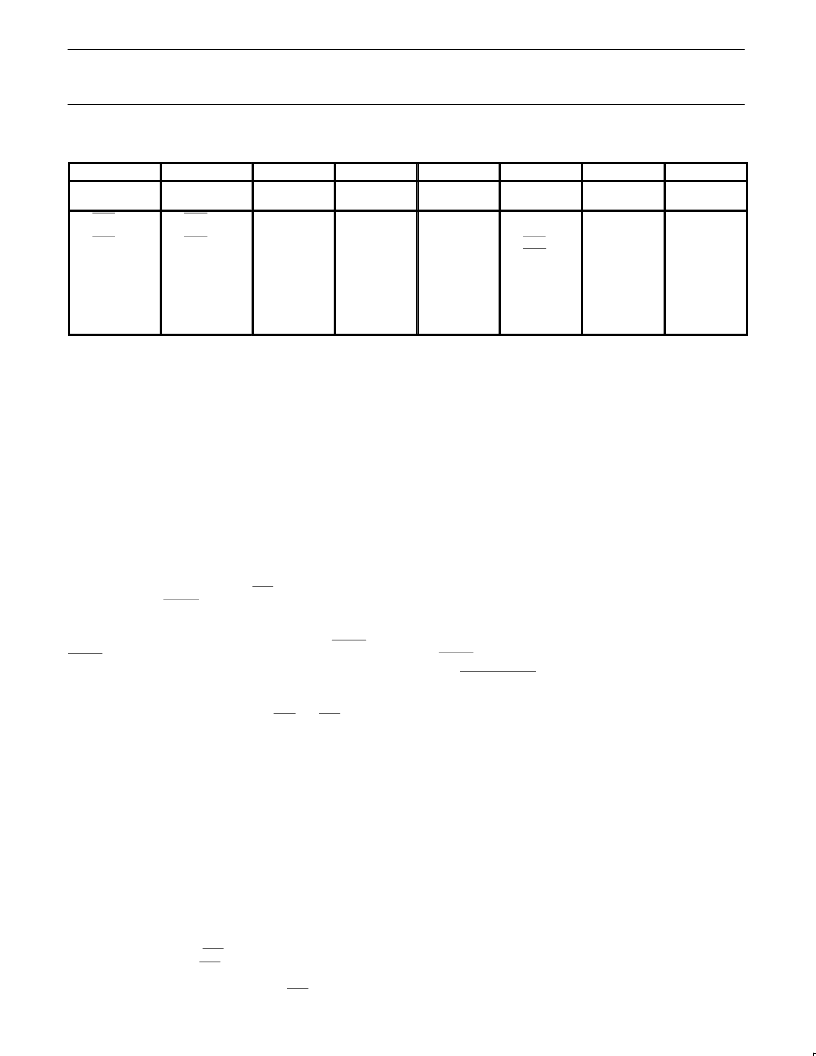

Table 8.

Status Register (SR)

SR7

SR6

SR5

SR4

SR3

SR2

SR1

SR0

Data Set

Ready

0 = DSR input

is High

1 = DSR input

is Low

Data Carrier

Detect

0 = DCD input

is High

1 = DCD input

is Low

FE/SYN

Detect

Async:

0 = Normal

1 = Framing

error

Overrun

PE/DLE

Detect

Async:

0 = Normal

1 = Parity error

TxEMT

DSCHG

0 = Normal

1 = Change in

DSR or

DCD, or

transmit

shift

register is

empty

RxRDY

TxRDY

Sync:

0 = Normal

1 = SYN

detected

0 = Normal

1 = Overrun

error

Sync:

0 = Normal

1 = Parity error

or DLE

received

0 = Receive

holding

register

empty

1 = Receive

holding

register

has data

0 = Transmit

holding

register

busy

1 = Transmit

holding

register

empty

Mode Register 2 (MR2)

Table 6 illustrates mode register 2. MR23, MR22, MR21 and MR20

control the frequency of the internal baud rate generator (BRG).

Sixteen rates are selectable for each EPCI version (–1,–2,–3).

Versions 1 and 2 specify a 4.9152MHz TTL input at BRCLK (pin 20);

version 3 specifies a 5.0688MHz input which is identical to the

Philips Semiconductors 2651. MR23 – 20 are don’t cares if external

clocks are selected (MR25 – MR24 = 0). The individual rates are

given in Table 1.

MR24 – MR27 select the receive and transmit clock source (either

the BRG or an external input) and the function at pins 9 and 25.

Refer to Table 6.

Command Register (CR)

Table 7 illustrates the command register. Bits CR0 (TxEN) and CR2

(RxEN) enable or disable the transmitter and receiver respectively.

A 0– to–1 transition of CR2 forces start bit search (async mode) or

hunt mode (sync mode) on the second RxC rising edge. Disabling

the receiver causes RxRDY to go High (inactive). If the transmitter

is disabled, it will complete the transmission of the character in the

transmit shift register (if any) prior to terminating operation. The TxD

output will then remain in the marking state (High) while TxRDY and

TxEMT will go High (inactive). If the receiver is disabled, it will

terminate operation immediately. Any character being assembled

will be neglected. A 0–to–1 transition of CR2 will initiate start bit

search (async) or hunt mode (sync).

Bits CR1 (DTR) and CR5 (RTS) control the DTR and RTS outputs.

Data at the outputs are the logical complement of the register data.

In asynchronous mode, setting CR3 will force and hold the TxD

output Low (spacing condition) at the end of the current transmitted

character. Normal operation resumes when CR3 is cleared. The

TxD line will go High for at least one bit time before beginning

transmission of the next character in the transmit data holding

register. In synchronous mode, setting CR3 causes the

transmission of the DLE register contents prior to sending the

character in the transmit data holding register. Since this is a one

time command, CR3 does not have to be reset by software. CR3

should be set when entering and exiting transparent mode and for

all DLE-non-DLE character sequences.

Setting CR4 causes the error flags in the status register (SR3, SR4,

and SR5) to be cleared; this is a one time command. There is no

internal latch for this bit.

When CR5 (RTS) is set, the RTS pin is forced Low. A 1–to–0

transition of CR5 will cause RTS to go High (inactive) one TxC time

after the last serial bit has been transmitted. If a 1–to–0 transition

of CR5 occurs while data is being transmitted, RTS will remain Low

(active) until both the THR and the transmit shift register are empty

and then go High (inactive) one TxC time later.

The EPCI can operate in one of four submodes within each major

mode (synchronous or asynchronous). The operational sub-mode is

determined by CR7 and CR6. CR7 – CR6 = 00 is the normal mode,

with the transmitter and receive operating independently in

accordance with the mode and status register instructions.

In asynchronous mode, CR7 – CR6 = 01 places the EPCI in the

automatic echo mode. Clocked, regenerated received data are

automatically directed to the TxD line while normal receiver

operation continues. The receiver must be enabled (CR2 = 1), but

the transmitter need not be enabled. CPU to receiver

communication continues normally, but the CPU to transmitter link is

disabled. Only the first character of a break condition is echoed.

The TxD output will go High until the next valid start is detected.

The following conditions are true while in automatic echo mode:

1. Data assembled by the receiver are automatically placed in the

transmit holding register and retransmitted by the transmitter on

the TxD output.

2. The transmitter is clocked by the receive clock.

3. TxRDY

output = 1.

4. The TxEMT/DSCHG pin will reflect only the data set change

condition.

5. The TxEN command (CR0) is ignored.

In synchronous mode, CR7 – CR6 = 01 places the EPCI in the

automatic SYN/DLE stripping mode. The exact action taken

depends on the setting of bits MR17 and MR16:

1. In the non-transparent, single SYN mode (MR17 – MR16 = 10),

characters in the data stream matching SYN1 are not transferred

to the Receive Data Holding register (RHR).

2. In the non-transparent, double SYN mode (MR17 – MR16 = 00),

character in the data stream matching SYN1, or SYN2 if immedi-

ately preceded by SYN1, are not transferred the RHR.

3. In transparent mode (MR16 = 1), character in the data stream

matching DLE, or SYN1 if immediately preceded by DLE, are not

transferred to the RHR. However, only the first DLE of a DLE–

DLE pair is stripped.

Note that automatic stripping mode does not affect the setting of the

DLE detect and SYN detect status bits (SR3 and SR5).

Two diagnostic sub-modes can also be configured. In local

loopback mode (CR7 – CR6 = 10), the following loops are

connected internally:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCN2661BA1F28 | Enhanced programmable communications interface EPCI |

| SCN2661AC1A28 | Enhanced programmable communications interface EPCI |

| SCN2661AC1N28 | Enhanced programmable communications interface EPCI |

| SCN2661BC1A28 | Enhanced programmable communications interface EPCI |

| SCN2661BC1F28 | Enhanced programmable communications interface EPCI |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCN68681 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual asynchronous receiver/transmitter DUART |

| SCN68681C1A44 | 制造商:PHILIPS 功能描述:SCN68681C1A44 制造商:NXP Semiconductors 功能描述: 制造商:NXP Semiconductors 功能描述:UART, 44 Pin, Plastic, PLCC |

| SCN68681C1N40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual asynchronous receiver/transmitter DUART |

| SCN68681E1A44 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual asynchronous receiver/transmitter DUART |

| SCN68681E1F40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual asynchronous receiver/transmitter DUART |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。