- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385813 > SAA6713AH (NXP Semiconductors N.V.) XGA analog input flat panel controller PDF資料下載

參數(shù)資料

| 型號(hào): | SAA6713AH |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | XGA analog input flat panel controller |

| 中文描述: | 模擬輸入的XGA液晶控制器 |

| 文件頁(yè)數(shù): | 7/100頁(yè) |

| 文件大小: | 498K |

| 代理商: | SAA6713AH |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)

2004 Apr 05

7

Philips Semiconductors

Product specification

XGA analog input flat panel controller

SAA6713AH

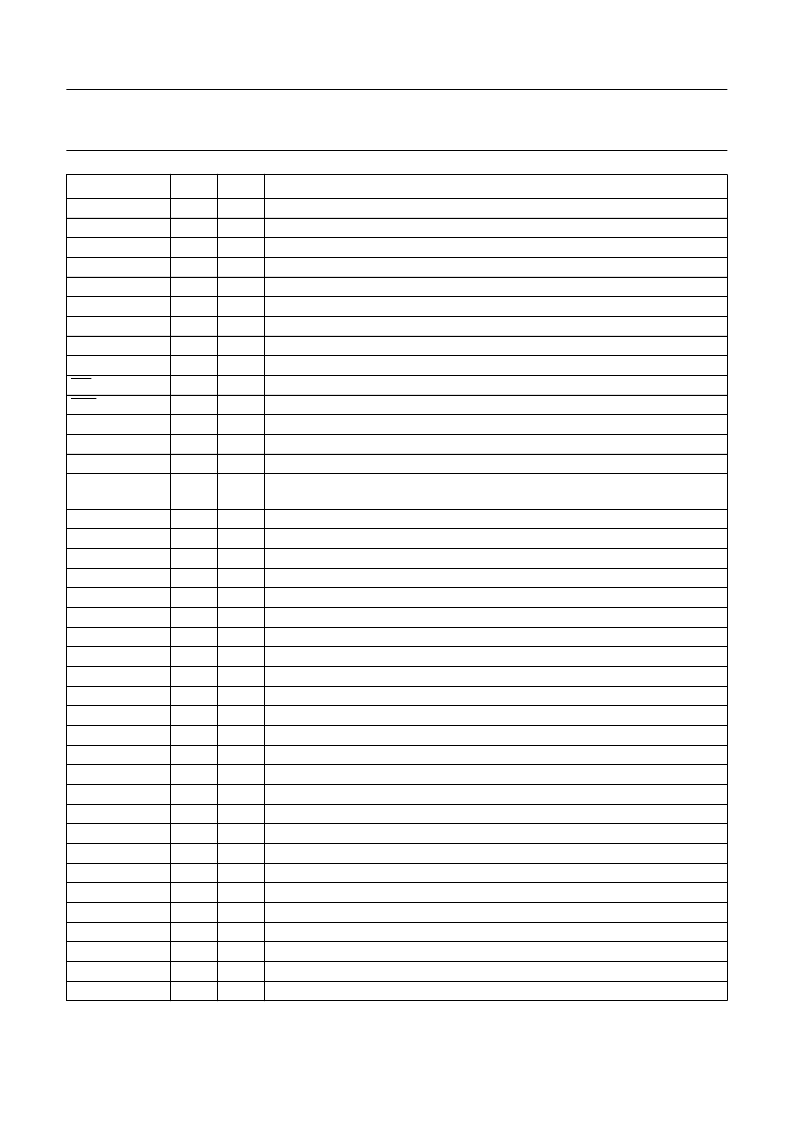

SDA

SCL

RESERVED2

RESERVED3

V

SSD(IC4)

V

DDD(IC4)

CLK

V

SSD(EP1)

V

DDD(EP1)

INT

RST

PCLK

CSG0

CSG1

CSG2/A0

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

I/O

I

I

O

I

O

O

O

I/O

serial data input or output (I

2

C-bus)

serial clock input (I

2

C-bus)

connect with a pull-up resistor of 4.7 k

to V

DDE

(3.3 or 5 V)

connect with a pull-up resistor of 4.7 k

to V

DDE

(3.3 or 5 V)

internal digital core supply ground 4

internal digital core supply voltage 4 (2.5 V)

master clock input

external digital pad supply ground 1

external digital pad supply voltage 1 (3.3 V)

microcontroller interrupt output (active LOW)

master reset input (active LOW)

panel clock output

control signal generator 0 output

control signal generator 1 output

control signal generator 2 output (CSG2) or I

2

C-bus slave address input, latched

via hardware reset (A0)

external digital pad supply ground 2

external digital pad supply voltage 2 (3.3 V)

panel data port A bit 0

panel data port A bit 1

panel data port A bit 2

panel data port A bit 3

panel data port A bit 4

panel data port A bit 5

panel data port A bit 6

panel data port A bit 7

external digital pad supply ground 3

external digital pad supply voltage 3 (3.3 V)

panel data port B bit 0

panel data port B bit 1

internal digital core supply ground 5

internal digital core supply voltage 5 (2.5 V)

panel data port B bit 2

panel data port B bit 3

panel data port B bit 4

panel data port B bit 5

panel data port B bit 6

panel data port B bit 7

external digital pad supply ground 4

external digital pad supply voltage 4 (3.3 V)

panel data port C bit 0

V

SSD(EP2)

V

DDD(EP2)

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

V

SSD(EP3)

V

DDD(EP3)

PB0

PB1

V

SSD(IC5)

V

DDD(IC5)

PB2

PB3

PB4

PB5

PB6

PB7

V

SSD(EP4)

V

DDD(EP4)

PC0

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

SYMBOL

PIN

(1)

TYPE

DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA6713H | XGA dual input flat panel controller |

| SAA7110 | Digital Multistandard Colour Decoder(數(shù)字多標(biāo)準(zhǔn)彩色譯碼器) |

| SAA7111 | Video Input Processor VIP |

| SAA7120H | Digital video encoder |

| SAA7152 | Digital Video Comb Filter DCF |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA6713AH/V1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:XGA analog input flat panel controller |

| SAA6713H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:XGA dual input flat panel controller |

| SAA6713H/V1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:XGA dual input flat panel controller |

| SAA6721 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SXGA RGB to TFT graphics engine |

| SAA6721E | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SXGA RGB to TFT graphics engine |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。