- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374571 > RC32434-400BC (Integrated Device Technology, Inc.) IDT TInterprise Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號(hào): | RC32434-400BC |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | IDT TInterprise Integrated Communications Processor |

| 中文描述: | IDT公司TInterprise集成通信處理器 |

| 文件頁(yè)數(shù): | 19/53頁(yè) |

| 文件大?。?/td> | 444K |

| 代理商: | RC32434-400BC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

19 of 53

January 19, 2006

IDT RC32434

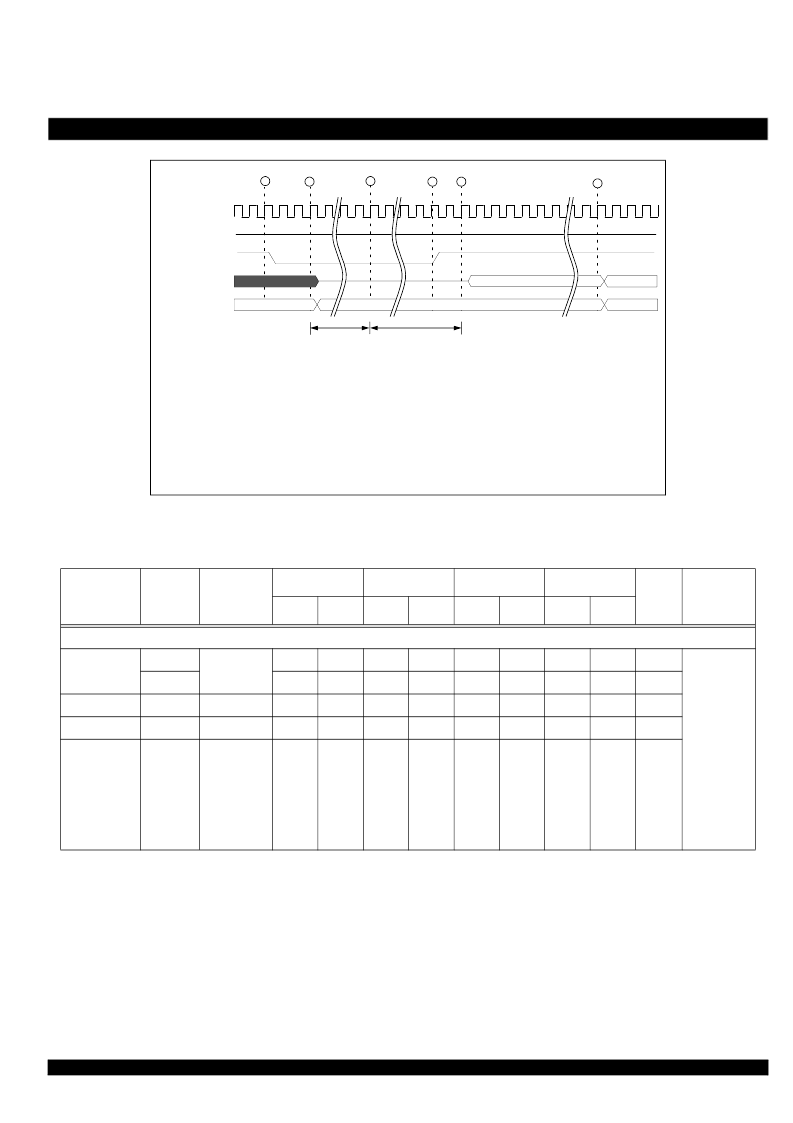

Figure 5 Externally Initiated Warm Reset AC Timing Waveform

S ignal

S ymbol

Referenc e

Edge

266MHz

300MHz

350MHz

400MHz

Unit

T iming

Diagram

Referenc e

Mn

Max

Mn

Max

Min

Max

Mn

Max

Memory Bus - DDR Access

DDRDATA[15:0]

Tskew_7g

DDRDQSx

0

0.9

0

0.8

1

1.

Meets DDR timng requirements for 150MHz clock rate DDR SDRAMs with 300 ps remaining margin to compensate for PCB propagation msmatches, which is adequate to

guarantee functional timng, provided the RC32434 DDR layout guidelines are adhered to.

2.

Setup times are calculated as applicable clock period - Tdo max. For example, if the DDR is running at 266MHz, it uses a 133MHz input clock. The period for a 133MHz clock

is 7.5ns. If the Tdo max value is 4.6ns, the T

IS

parameter is 7.5ns mnus 4.6ns = 2.9ns. The DDR spec for this parameter is 1ns, so there is 1.9ns of slack left over for board

propagation. Calculations for T

DS

are simlar, but since this parameter is taken relative to the DDRDQS signals, which are referenced on both edges, the effective period with

a 133MHz input clock is only 3.75ns. So, if the max Tdo is 1.9ns, we have 3.75ns mnus 1.9ns = 1.85ns for T

DS

. The DDR data sheet specs a value of 0.5ns for 266MHz, so

this leaves 1.35ns slack for board propagation delays.

0

0.7

0.0

0.6

ns

See Figures 6

and 7.

Tdo_7k

2

1.2

1.9

1.0

1.7

0.7

1.5

0.5

1.4

ns

DDRDM[1:0]

Tdo_7l

DDRDQSx

1.2

1.9

1.0

1.7

0.7

1.5

0.5

1.4

ns

DDRDQS[1:0]

Tdo_7i

DDRCKP

-0.75

0.75

-0.75

0.75

-0.7

0.7

-0.7

0.7

ns

DDRADDR[13:0],

DDRBA[1:0],

DDRCASN,

DDRCKE,

DDRCSN,

DDRRASN,

DDRWEN

Tdo_7m

DDRCKP

1.0

4.0

1.0

4.3

1.0

4.0

1.0

4.0

ns

Table 7 DDR SDRAMTiming Characteristics

1.

Warmreset condition caused by assertion of RSTN by an external agent.

2.

The RC32434 tri-states the data bus, MDATA[7:0], negates all memory control signals, and itself asserts RSTN. The RC32434 continues to

drive the address bus throughout the entire warmreset.

3.

The RC32434 negates RSTN after 4000 master clock (CLK) clock cycles.

4.

External logic negates RSTN.

5.

The RC32434 samples RSTN negated at least 4000 master clock (CLK) clock cycles after step 3 and starts driving the data bus,

MDATA[7:0].

6.

CPU begins executing by taking a MIPS soft reset exception. The assertion of CSN[0] will occur no sooner than 16 clock cycles after the

RC32434 samples RSTN negated (i.e., step 5).

Active

Deasserted

Active

CLK

COLDRSTN

RSTN

MDATA[7:0]

MemControl Signals

FFFF_FFFF

1

2

4

5

6

3

≥

4000 CLK

clock Cycles

≥

4000 CLK

clock Cycles

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RC32434-400BCI | IDT TInterprise Integrated Communications Processor |

| RC3403A | Ground Sensing Quad Operational Amplifier |

| RC3403AN | Ground Sensing Quad Operational Amplifier |

| RC4152 | Voltage-to-Frequency Converters |

| RC4152M | Voltage-to-Frequency Converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RC32434-400BCI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT TInterprise Integrated Communications Processor |

| RC3-25V220M | 制造商:ELNA America Inc 功能描述: |

| RC3-25V220MF0#-T58 | 制造商:ELNA America Inc 功能描述: |

| RC3-25V220MGZ-T58 | 制造商:ELNA America Inc 功能描述: |

| RC326F244J | 制造商:Rockwell Automation / Allen-Bradley 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。