- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374571 > RC32434-350BCI (Integrated Device Technology, Inc.) IDT TInterprise Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號(hào): | RC32434-350BCI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | IDT TInterprise Integrated Communications Processor |

| 中文描述: | IDT公司TInterprise集成通信處理器 |

| 文件頁(yè)數(shù): | 9/53頁(yè) |

| 文件大小: | 444K |

| 代理商: | RC32434-350BCI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

9 of 53

January 19, 2006

IDT RC32434

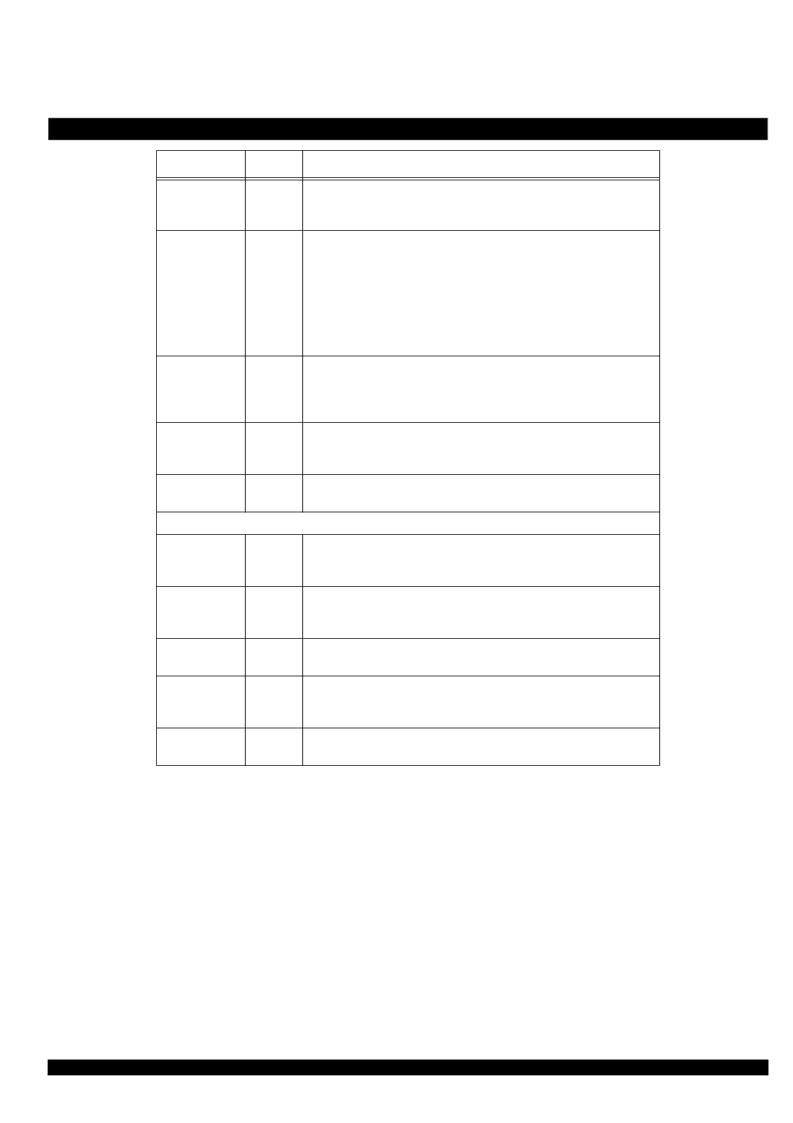

Pin Charac teristic s

Note:

Some input pads of the RC32434 do not contain internal pull-ups or pull-downs. Unused inputs should be tied off to appropriate

levels. This is especially critical for unused control signal inputs (such as WAITACKN) which, if left floating, could adversely affect the

RC32434’s operation. Also, any input pin left floating can cause a slight increase in power consumption.

EJTAG_TMS

I

EJTAG Mode

. The value on this signal controls the test mode select of the

EJTAG Controller. When using the JTAG boundary scan, this pin should be left

disconnected (since there is an internal pull-up) or driven high.

JTAG_TRST_N

I

JTAG Reset

. This active low signal asynchronously resets the boundary scan

logic, JTAG TAP Controller, and the EJTAG Debug TAP Controller. An external

pull-up on the board is recommended to meet the JTAG specification in cases

where the tester can access this signal. However, for systems running in func-

tional mode, one of the following should occur:

1) actively drive this signal low with control logic

2) statically drive this signal low with an external pull-down on the board

3) clock JTAG_TCK while holding EJTAG_TMS and/or JTAG_TMS high.

JTAG_TCK

I

JTAG Clock

. This is an input test clock used to clock the shifting of data into or

out of the boundary scan logic, JTAG Controller, or the EJTAG Controller.

JTAG_TCK is independent of the systemand the processor clock with a nom-

nal 50% duty cycle.

JTAG_TDO

O

JTAG Data Output

. This is the serial data shifted out fromthe boundary scan

logic, JTAG Controller, or the EJTAG Controller. When no data is being shifted

out, this signal is tri-stated.

JTAG_TDI

I

JTAG Data Input

. This is the serial data input to the boundary scan logic, JTAG

Controller, or the EJTAG Controller.

System

CLK

I

Master Clock.

This is the master clock input. The processor frequency is a mul-

tiple of this clock frequency. This clock is used as the systemclock for all mem-

ory and peripheral bus operations.

EXTBCV

I

Load External Boot Configuration Vector.

When this pin is asserted (i.e.,

high) the boot configuration vector is loaded froman externally supplied value

during a cold reset.

EXTCLK

O

External Clock.

This clock is used for all memory and peripheral bus opera-

tions.

COLDRSTN

I

Cold Reset.

The assertion of this signal initiates a cold reset. This causes the

processor state to be initialized, boot configuration to be loaded, and the internal

PLL to lock onto the master clock (CLK).

RSTN

I/O

Reset.

The assertion of this bidirectional signal initiates a warmreset. This sig-

nal is asserted by the RC32434 during a warmreset.

S ignal

Type

Name/Desc ription

Table 1 Pin Description (Part 6 of 6)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RC32434-400BC | IDT TInterprise Integrated Communications Processor |

| RC32434-400BCI | IDT TInterprise Integrated Communications Processor |

| RC3403A | Ground Sensing Quad Operational Amplifier |

| RC3403AN | Ground Sensing Quad Operational Amplifier |

| RC4152 | Voltage-to-Frequency Converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RC32434-400BC | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT TInterprise Integrated Communications Processor |

| RC32434-400BCI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT TInterprise Integrated Communications Processor |

| RC3-25V220M | 制造商:ELNA America Inc 功能描述: |

| RC3-25V220MF0#-T58 | 制造商:ELNA America Inc 功能描述: |

| RC3-25V220MGZ-T58 | 制造商:ELNA America Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。