- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11788 > PI7C8150BMAE (Pericom)IC PCI-PCI BRIDGE ASYNC 208-FQFP PDF資料下載

參數(shù)資料

| 型號: | PI7C8150BMAE |

| 廠商: | Pericom |

| 文件頁數(shù): | 64/109頁 |

| 文件大小: | 0K |

| 描述: | IC PCI-PCI BRIDGE ASYNC 208-FQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | * |

| 應(yīng)用: | * |

| 接口: | * |

| 電源電壓: | * |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-FQFP(28x28) |

| 包裝: | 管件 |

| 安裝類型: | 表面貼裝 |

| 產(chǎn)品目錄頁面: | 1227 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁當(dāng)前第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁

PI7C8150B

ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE

ADVANCE INFORMATION

Page 58 of 109

April 2009 – Revision 1.08

Primary

Data

Parity Bit

Transaction Type

Direction

Bus Where Error

Was Detected

Primary /

Secondary Parity

Error Response

Bits

0

Delayed Write

Upstream

Secondary

x / x

X = don’t care

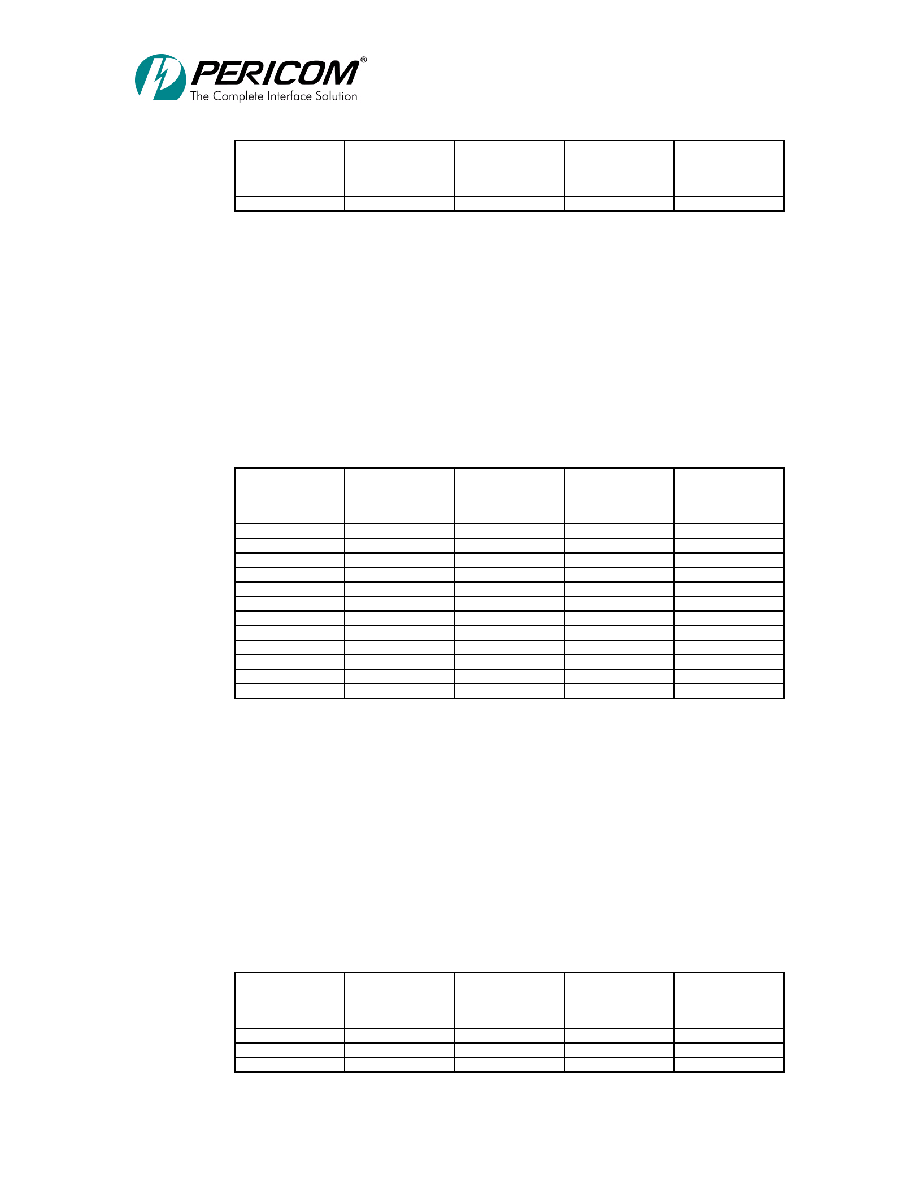

Table 6-4 shows setting the data parity detected bit in the status register of secondary

interface. This bit is set under the following conditions:

The PI7C8150B must be a master on the secondary bus.

The parity error response bit must be set in the bridge control register of secondary

interface.

The S_PERR_L signal is detected asserted or a parity error is detected on the

secondary bus.

Table 6-4. Setting Secondary Interface Master Data Parity Error Detected Bit

Secondary

Detected

Parity

Detected Bit

Transaction Type

Direction

Bus Where Error

Was Detected

Primary /

Secondary Parity

Error Response

Bits

0

Read

Downstream

Primary

x / x

1

Read

Downstream

Secondary

x / 1

0

Read

Upstream

Primary

x / x

0

Read

Upstream

Secondary

x / x

0

Posted Write

Downstream

Primary

x / x

1

Posted Write

Downstream

Secondary

x / 1

0

Posted Write

Upstream

Primary

x / x

0

Posted Write

Upstream

Secondary

x / x

0

Delayed Write

Downstream

Primary

x / x

1

Delayed Write

Downstream

Secondary

x / 1

0

Delayed Write

Upstream

Primary

x / x

0

Delayed Write

Upstream

Secondary

x / x

X= don’t care

Table 6-5 shows assertion of P_PERR_L. This signal is set under the following

conditions:

PI7C8150B is either the target of a write transaction or the initiator of a read

transaction on the primary bus.

The parity-error-response bit must be set in the command register of primary interface.

PI7C8150B detects a data parity error on the primary bus or detects S_PERR_L

asserted during the completion phase of a downstream delayed write transaction on the

target (secondary) bus.

Table 6-5. Assertion of P_PERR_L

P_PERR_L

Transaction Type

Direction

Bus Where Error

Was Detected

Primary/

Secondary Parity

Error Response

Bits

1 (de-asserted)

Read

Downstream

Primary

x / x

1

Read

Downstream

Secondary

x / x

0 (asserted)

Read

Upstream

Primary

1 / x

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| D38999/26FD15PA | CONN PLUG 15POS STRAIGHT W/PINS |

| D38999/20MC8SN | CONN RCPT 8POS WALL MNT W/SCKT |

| D38999/20MD18SN | CONN RCPT 18POS WALL MNT W/SCKT |

| 0510210700 | CONN HOUSING 7POS 1.25MM |

| ADN8102ACPZ | IC EQUALIZER 4CH XSTREAM 64LFCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8150BMAI | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE |

| PI7C8150BMAI-33 | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE |

| PI7C8150BMAIE | 功能描述:外圍驅(qū)動器與原件 - PCI 2 Port 32B PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8150BMAIE-33 | 功能描述:外圍驅(qū)動器與原件 - PCI 2 Port 32B PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8150BND | 功能描述:外圍驅(qū)動器與原件 - PCI 2-Port 32-Bit PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。