- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382380 > PCD5043 (NXP Semiconductors N.V.) DECT burst mode controller PDF資料下載

參數(shù)資料

| 型號(hào): | PCD5043 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | DECT burst mode controller |

| 中文描述: | 無(wú)繩突發(fā)模式控制器 |

| 文件頁(yè)數(shù): | 13/24頁(yè) |

| 文件大小: | 109K |

| 代理商: | PCD5043 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

1996 Oct 31

13

Philips Semiconductors

Objective specification

DECT burst mode controller

PCD5043

6.5.7

L

OCAL CALL SWITCHING

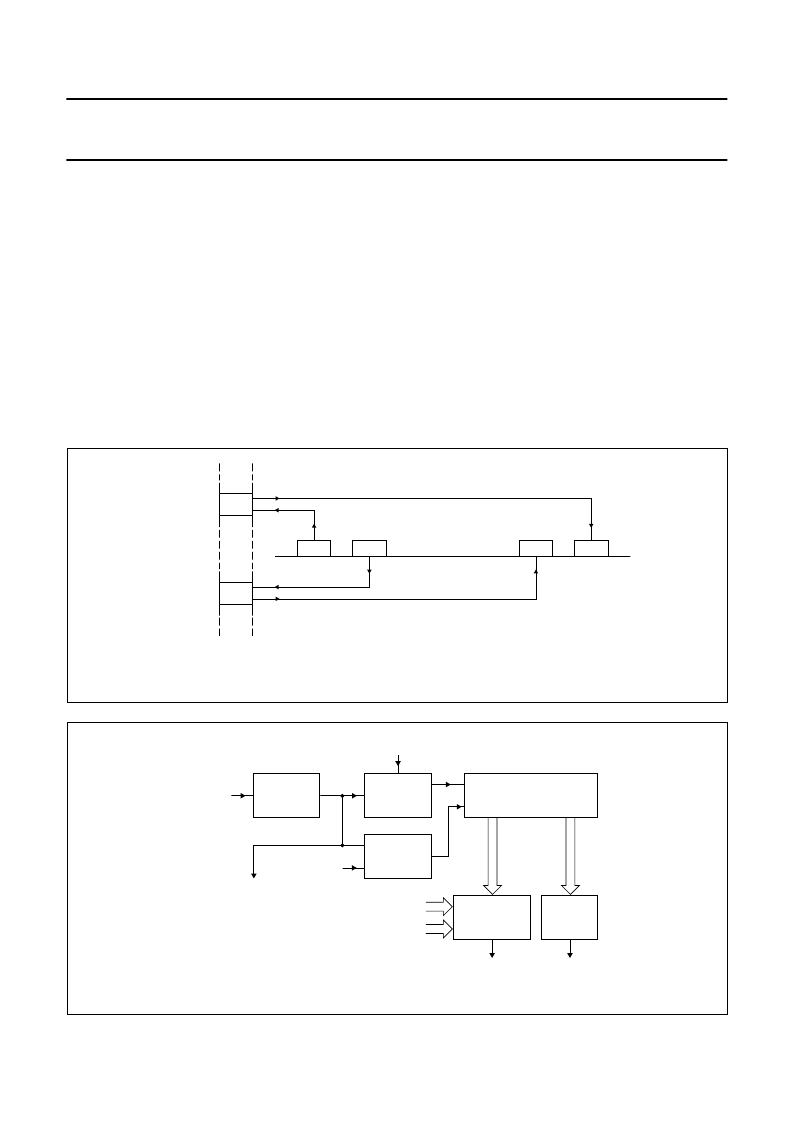

(see Fig.8)

The PCD5043 provides a local call switching function in

the base station. It will store incoming speech nibbles in

the common data memory, in the area reserved for that

particular receive slot. Then, during the transmit phase, it

passes the start pointer of the same data memory area to

the transmit block. Thus, the speech data is echoed to the

other user. To handle quality degradation for local calls, a

mute can be performed at the RF side of the speech buffer.

6.5.8

D

ATA SYNCHRONIZATION

(see Fig.9)

The data synchronization is done in 2 phases:

Bit synchronization

Sync word detection.

Bit synchronization is done using a Digital PLL (DPLL),

with an oversampling factor of 12, i.e. the DPLL is running

at 12 times the data rate. The output from the DPLL is a

receive clock signal (RxC), which acts as the enable for a

20-bit shift register.

Sync word detection is achieved by checking the incoming

data pattern with the expected synchronization field

pattern, using a correlator.

The correlator has a programmable threshold, so it can

accept bit errors in the sync field pattern up to the

threshold level. Furthermore, the correlator window is

programmable. This means that ‘SlotSync’, which

indicates the slot synchronization event, can be detected

only during a certain period (the time window).

Fig.8 Local call switching on the RF-side.

handbook, full pagewidth

MBH712

Rx1

speech buffers

in data memory

Rx2

Tx1

Tx2

RF slots

Fig.9 Schematic of the receiver synchronization part.

handbook, full pagewidth

MBH713

threshold

base/handset

CORRELATOR

(E98A)

Q0 to Q15

EN

R

×

C

D

filtered

data in

R_DATA

(1152 kbits/s)

to serial

receiver logic

FILTER

DPLL

13.824 MHz

XOR

20-BIT SHIFT

REGISTER

Q16 to Q19

SlotSync

correlator

window

SYNC

CHECK

(1010)

DPLL_sync

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD5043H | DECT burst mode controller |

| PCD5091HZ | DECT baseband controller |

| PCD5091 | DECT baseband controller |

| PCD5091H | DECT baseband controller |

| PCD5092 | DECT baseband controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD5043H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:DECT burst mode controller |

| PCD5071 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MODEM |

| PCD5090 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:DECT baseband controllers |

| PCD5090H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:DECT baseband controllers |

| PCD5090H232F1 | 制造商:PHILIPS 功能描述:* |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。