- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382368 > P82C150 (NXP Semiconductors N.V.) CAN Serial Linked I/O device SLIO with digital and analog port functions PDF資料下載

參數(shù)資料

| 型號(hào): | P82C150 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | CAN Serial Linked I/O device SLIO with digital and analog port functions |

| 中文描述: | CAN串行鏈接I / O與數(shù)字和模擬接口功能設(shè)備SLIO |

| 文件頁(yè)數(shù): | 17/36頁(yè) |

| 文件大小: | 209K |

| 代理商: | P82C150 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

1996 Jun 19

17

Philips Semiconductors

Preliminary specification

CAN Serial Linked I/O device (SLIO) with

digital and analog port functions

P82C150

7.3.4

CAN-

BUS MODES

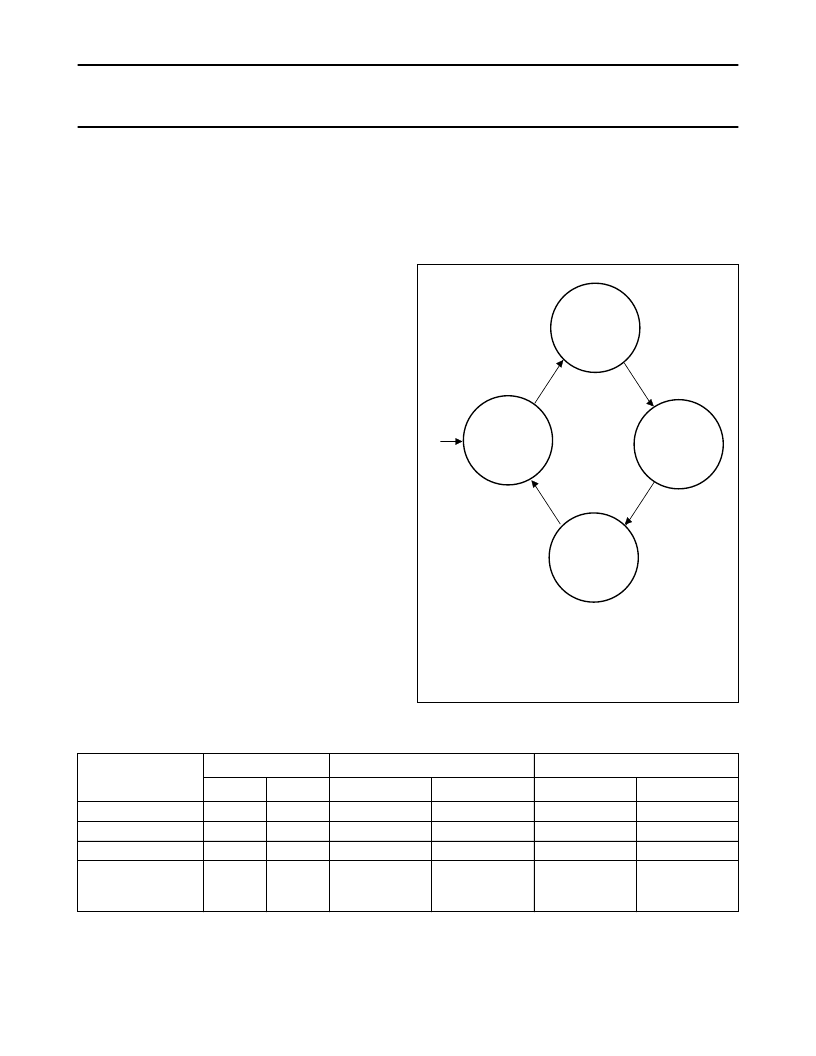

The P82C150 can pass through four CAN-bus modes

under certain conditions (see Fig.8). In the bus modes

0 to 2 (see Table 10) the P82C150 is operating with

different input comparator configurations. Bus mode 3 is

the power reduced Sleep Mode.

The bus modes support:

Communication on two balanced wires (differential

system)

Communication on one wire in a two-wire differential

system

Sleep Mode with wake-up via either a dominant signal

on RX0 or RX1 input

Connection of a second transmission medium

(redundancy)

There are two possibilities for condition 1 to switch to the

next mode (see Fig.8):

Overflow of the bit counter when 8192 is reached since

the last calibration message

Overflow of the Transmit Error Counter (>255; bus-off

limit reached).

When the bus mode changes, all I/O Registers are cleared

and outputs become floating (OE bits cleared). That

means the I/O ports return to a fail-safe state whenever the

P82C150 looses connection to its host controller. This is a

kind of network watchdog function. The status bits are set

to the following values after a bus mode change:

RSTD = 1

EW = 0

BM

new

= BM

old

+ 1.

The programmed Identifier bits remain unchanged.

After reset the P82C150 changes directly into bus mode 3

(Sleep Mode). During Sleep Mode, the internal RC

oscillator is stopped, and all the output drivers are disabled

(I/O Register contents cleared). A P82C150 in Sleep Mode

can be woken up via CAN-bus lines (dominant level on

RX0 or RX1) or by a reset condition.

Fig.8 CAN-bus modes and switch-over conditions.

columns

DIFFERENTIAL

MODE

Inputs: RX0, RX1

Outputs: TX0, TX1

'0'

ONE-WIRE

RX1 MODE

Input: RX1

Outputs: TX0, TX1

'1'

'2'

SLEEP

MODE

Inputs: RX0, RX1

Outputs: no

'3'

ONE-WIRE

RX0 MODE

Input: RX0

Output: TX0

Condition 1

Condition 1

Condition 1

Condition 2

MHA070

end of

RESET

Condition 1:

bit counter overflow (>8191) or Transmit Error Counter overflow (>255).

Condition 2:

dominant bit detected on RX0 and RX1.

Table 10

Can-bus modes

Note

1.

Output TX1 is disabled in bus mode 2 to tolerate short-circuit between the CAN-bus wires CAN_H and CAN_L.

BUS MODE

BITS

RECEPTION LEVEL

TRANSMISSION

BM1

BM0

RECESSIVE

DOMINANT

TX1

TX0

0 = Differential

1 = One-wire RX1

2 = One-wire RX0

3 = Sleep

0

0

1

1

0

1

0

1

RX0 > RX1

RX1 < REF

RX0 > REF

RX0 > REF

and

RX1 < REF

RX0 < RX1

RX1 > REF

RX0 < REF

RX0 < REF

or

RX1 > REF

enabled

enabled

disabled

disabled

enabled

enabled

enabled

disabled

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P82C150AFT | CAN Serial Linked I/O device SLIO with digital and analog port functions |

| P82C150AHT | 22 PIN R/A MALE PRESSFIT ATCA ZONE 1 CON |

| P82C605 | System Controller |

| P82C606 | System Controller |

| P82C607 | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P82C150AFT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CAN Serial Linked I/O device SLIO with digital and analog port functions |

| P82C150AHT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CAN Serial Linked I/O device SLIO with digital and analog port functions |

| P82C201-10 | 制造商:CHIPS 功能描述: 制造商:CHIP 功能描述:SYSTEM CONTROLLER, 84 Pin, PLCC 制造商:CHIPS 功能描述:SYSTEM CONTROLLER, 84 Pin, PLCC |

| P82C201-10 TS89 | 制造商:TOS 功能描述:82C201-10 |

| P82C201-10-7014-0093 | 制造商:CHIPS 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。