- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299576 > OR3T165-4B432 FPGA, 1024 CLBS, 120000 GATES, PBGA432 PDF資料下載

參數(shù)資料

| 型號: | OR3T165-4B432 |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 1024 CLBS, 120000 GATES, PBGA432 |

| 封裝: | BGA-432 |

| 文件頁數(shù): | 126/210頁 |

| 文件大?。?/td> | 2138K |

| 代理商: | OR3T165-4B432 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁當(dāng)前第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁

22

Lucent Technologies Inc.

Preliminary Data Sheet, Rev. 1

ORCA Series 3 FPGAs

September 1998

Programmable Logic Cells (continued)

PLC Latches/Flip-Flops

The eight general-purpose latches/FFs in the PFU can

be used in a variety of configurations. In some cases,

the configuration options apply to all eight latches/FFs

in the PFU and some apply to the latches/FFs on a nib-

ble-wide basis where the ninth FF is considered inde-

pendently. For other options, each latch/FF is

independently programmable. In addition, the ninth FF

can be used for a variety of functions.

Table 7 summarizes these latch/FF options. The

latches/FFs can be configured as either positive or

negative level sensitive latches, or positive or negative

edge-triggered flip-flops (the ninth register can only be

FF). All latches/FFs in a given PFU share the same

clock, and the clock to these latches/FFs can be

inverted. The input into each latch/FF is from either the

corresponding LUT output (F[7:0]) or the direct data

input (DIN[7:0]). The latch/FF input can also be tied to

logic 1 or to logic 0, which is the default.

* Not available for FF[8].

The eight latches/FFs in a PFU share the clock (CLK)

and options for clock enable (CE), local set/reset

(LSR), and front-end data select (SEL) inputs. When

CE is disabled, each latch/FF retains its previous value

when clocked. The clock enable, LSR, and SEL inputs

can be inverted to be active-low.

The set/reset operation of the latch/FF is controlled by

two parameters: reset mode and set/reset value. When

the global set/reset (GSRN) and local set/reset (LSR)

signals are not asserted, the latch/FF operates nor-

mally. The reset mode is used to select a synchronous

or asynchronous LSR operation. If synchronous, LSR

has the option to be enabled only if clock enable (CE or

ASWE) is active or for LSR to have priority over the

clock enable input, thereby setting/resetting the FF

independent of the state of the clock enable. The clock

enable is supported on FFs, not latches. It is imple-

mented by using a 2-input multiplexer on the FF input,

with one input being the previous state of the FF and

the other input being the new data applied to the FF.

The select of this 2-input multiplexer is clock enable

(CE or ASWE), which selects either the new data or the

previous state. When the clock enable is inactive, the

FF output does not change when the clock edge

arrives.

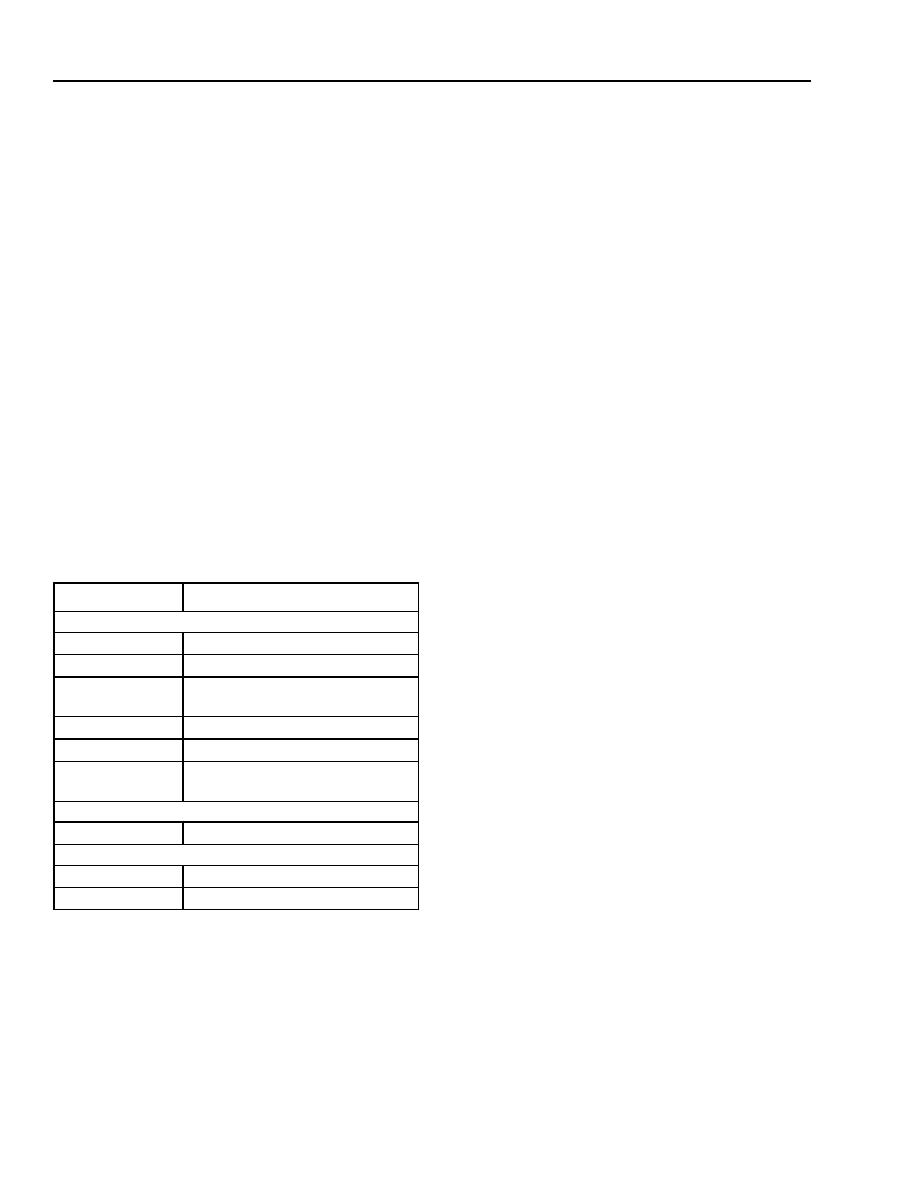

Table 7. Configuration RAM Controlled Latch/

Flip-Flop Operation

Function

Options

Common to All Latches/FFs in PFU

LSR Operation

Asynchronous or synchronous

Clock Polarity

Noninverted or inverted

Front-end Select*

Direct (DIN[7:0]) or from LUT

(F[7:0])

LSR Priority

Either LSR or CE has priority

Latch/FF Mode

Latch or flip-flop

Enable GSRN

GSRN enabled or has no effect on

PFU latches/FFs

Set Individually in Each Latch/FF in PFU

Set/Reset Mode

Set or reset

By Group (Latch/FF[3:0], Latch/FF[7:4], and FF[8])

Clock Enable

CE or ASWE or none

LSR Control

LSR or none

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR3T165-4B600 | FPGA, 1024 CLBS, 120000 GATES, PBGA600 |

| OR3T165-4BA352I | FPGA, 1024 CLBS, 120000 GATES, PBGA352 |

| OR3T165-4BA352 | FPGA, 1024 CLBS, 120000 GATES, PBGA352 |

| OR3T165-4BC432I | FPGA, 1024 CLBS, 120000 GATES, PBGA432 |

| OR3T165-4BC600I | FPGA, 1024 CLBS, 120000 GATES, PBGA600 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR3T20 | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T20-4BA256I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T20-4S208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T20-4S240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T20-5BA256 | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。