- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383723 > OR2T40B (Lattice Semiconductor Corporation) Field-Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號: | OR2T40B |

| 廠商: | Lattice Semiconductor Corporation |

| 元件分類: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 現(xiàn)場可編程門陣列 |

| 文件頁數(shù): | 48/192頁 |

| 文件大小: | 935K |

| 代理商: | OR2T40B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁

48

Lattice Semiconductor

Data Sheet

January 2002

ORCA

Series 2 FPGAs

FPGA Configuration Modes

(continued)

Master Serial Mode

In the master serial mode, the FPGA loads the con

fi

gu-

ration data from an external serial ROM. The con

fi

gura-

tion data is either loaded automatically at start-up or on

a

PRGM

command to recon

fi

gure. The ATT1700 and

ATT1700A Series can be used to con

fi

gure the FPGA

in the master serial mode. This provides a simple 4-pin

interface in an 8-pin package. The ATT1736, ATT1765,

and ATT17128 serial ROMs store 32K, 64K, and 128K

bits, respectively.

Con

fi

guration in the master serial mode can be done at

powerup and/or upon a con

fi

gure command. The sys-

tem or the FPGA must activate the serial ROM's

RESET

/OE and

CE

inputs. At powerup, the FPGA and

serial ROM each contain internal power-on reset cir-

cuitry that allows the FPGA to be con

fi

gured without

the system providing an external signal. The power-on

reset circuitry causes the serial ROM's internal address

pointer to be reset. After powerup, the FPGA automati-

cally enters its initialization phase.

The serial ROM/FPGA interface used depends on such

factors as the availability of a system reset pulse, avail-

ability of an intelligent host to generate a con

fi

gure

command, whether a single serial ROM is used or mul-

tiple serial ROMs are cascaded, whether the serial

ROM contains a single or multiple con

fi

guration pro-

grams, etc. Because of differing system requirements

and capabilities, a single FPGA/serial ROM interface is

generally not appropriate for all applications.

Data is read in the FPGA sequentially from the serial

ROM. The DATA output from the serial ROM is con-

nected directly into the DIN input of the FPGA. The

CCLK output from the FPGA is connected to the

CLOCK input of the serial ROM. During the con

fi

gura-

tion process, CCLK clocks one data bit on each rising

edge.

Since the data and clock are direct connects, the

FPGA/serial ROM design task is to use the system or

FPGA to enable the

RESET

/OE and

CE

of the serial

ROM(s). There are several methods for enabling the

serial ROM’s

RESET

/OE and

CE

inputs. The serial

ROM's

RESET

/OE is programmable to function with

RESET active-high and

OE

active-low or

RESET

active-

low and OE active-high.

In Figure 41, serial ROMs are cascaded to con

fi

gure

multiple daisy-chained FPGAs. The host generates a

500 ns low pulse into the FPGA's

PRGM

input. The

FPGA’s

INIT

input is connected to the serial ROM’s

RESET

/OE input, which has been programmed to

function with

RESET

active-low and OE active-high.

The FPGA DONE is routed to the

CE

pin. The low on

DONE enables the serial ROMs. At the completion of

con

fi

guration, the high on the FPGA's DONE disables

the serial ROM.

Serial ROMs can also be cascaded to support the con-

fi

guration of multiple FPGAs or to load a single FPGA

when con

fi

guration data requirements exceed the

capacity of a single serial ROM. After the last bit from

the

fi

rst serial ROM is read, the serial ROM outputs

CEO

low and 3-states the DATA output. The next serial

ROM recognizes the low on

CE

input and outputs con-

fi

guration data on the DATA output. After con

fi

guration

is complete, the FPGA’s DONE output into

CE

disables

the serial ROMs.

This FPGA/serial ROM interface is not used in applica-

tions in which a serial ROM stores multiple con

fi

gura-

tion programs. In these applications, the next

con

fi

guration program to be loaded is stored at the

ROM location that follows the last address for the previ-

ous con

fi

guration program. The reason the interface in

Figure 41 will not work in this application is that the low

output on the

INIT

signal would reset the serial ROM

address pointer, causing the

fi

rst con

fi

guration to be

reloaded.

In some applications, there can be contention on the

FPGA's DIN pin. During con

fi

guration, DIN receives

con

fi

guration data, and after con

fi

guration, it is a user

I/O. If there is contention, an early DONE at start-up

(selected in

ORCA

Foundry) may correct the problem.

An alternative is to use

LDC

to drive the serial ROM's

CE

pin. In order to reduce noise, it is generally better to

run the master serial con

fi

guration at 1.25 MHz (M3 pin

tied high), rather than 10 MHz, if possible.

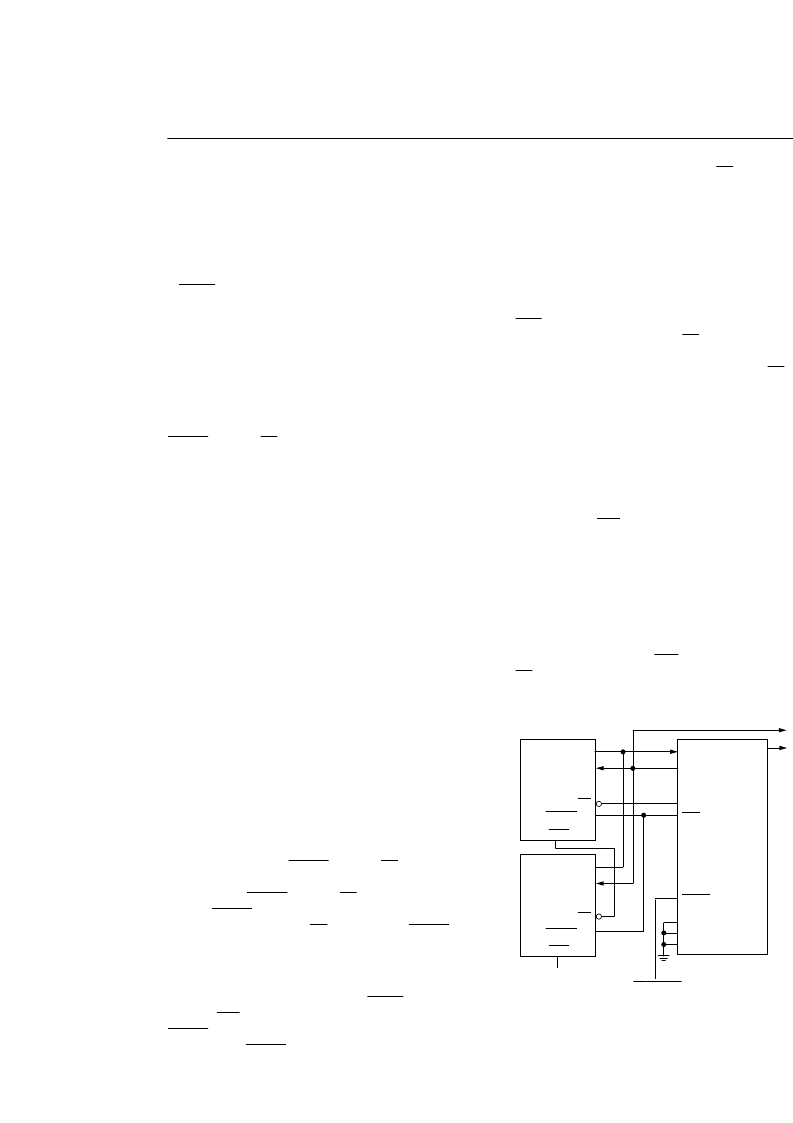

Figure 41. Master Serial Configuration Schematic

ATT1700A

DIN

M2

M1

M0

ORCA

SERIES

FPGA

CCLK

DOUT

TO DAISY-

CHAINED

DEVICES

DATA

CLK

CE

CEO

ATT1700A

DATA

CLK

RESET/OE

CEO

CE

TO MORE

SERIAL ROMs

AS NEEDED

DONE

INIT

PROGRAM

RESET/OE

PRGM

5-4456.1(F)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR2 | 2-input OR gate with 1x drive strength |

| OR3LP26B | Field-Programmable System Chip (FPSC) Embedded Master/Target PCI Interface |

| OR3TP12-6BA256 | Single 2.3V 10 MHz OP w/ CS, I temp, -40C to +85C, 8-TSSOP, T/R |

| OR3TP12-6BA256I | Single 2.3V 10 MHZ OP, -40C to +125C, 14-SOIC 150mil, TUBE |

| OR3TP12-6BA352 | Quad 2.3V 10 MHz OP, I temp, -40C to +85C, 14-PDIP, TUBE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR2T40B7BA352-DB | 功能描述:FPGA - 現(xiàn)場可編程門陣列 Use ECP/EC or XP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR2T40B7BA352I-DB | 功能描述:FPGA - 現(xiàn)場可編程門陣列 Use ECP/EC or XP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR2T40B7BC352-DB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| OR2T40B7BC432-DB | 功能描述:FPGA - 現(xiàn)場可編程門陣列 Use ECP/EC or XP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR2T40B7BC432I-DB | 功能描述:FPGA - 現(xiàn)場可編程門陣列 Use ECP/EC or XP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。