- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄189002 > NAND01GW4B3CZA1E (STMICROELECTRONICS) 64M X 16 FLASH 3V PROM, 35 ns, PBGA63 PDF資料下載

參數(shù)資料

| 型號(hào): | NAND01GW4B3CZA1E |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 64M X 16 FLASH 3V PROM, 35 ns, PBGA63 |

| 封裝: | 9.50 X 12 MM, 1 MM HEIGHT, 0.80 MM PITCH, ROHS COMPLIANT, VFBGA-63 |

| 文件頁數(shù): | 17/59頁 |

| 文件大?。?/td> | 998K |

| 代理商: | NAND01GW4B3CZA1E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

NAND512-B, NAND01G-B, NAND02G-B, NAND04G-B, NAND08G-B

24/59

Copy Back Program

The Copy Back Program operation is used to copy

the data stored in one page and reprogram it in an-

other page.

The Copy Back Program operation does not re-

quire external memory and so the operation is

faster and more efficient because the reading and

loading cycles are not required. The operation is

particularly useful when a portion of a block is up-

dated and the rest of the block needs to be copied

to the newly assigned block.

If the Copy Back Program operation fails an error

is signalled in the Status Register. However as the

standard external ECC cannot be used with the

Copy Back Program operation bit error due to

charge loss cannot be detected. For this reason it

is recommended to limit the number of Copy Back

Program operations on the same data and or to

improve the performance of the ECC.

The Copy Back Program operation requires four

steps:

1.

The first step reads the source page. The

operation copies all 1056 Words/ 2112 Bytes

from the page into the Data Buffer. It requires:

–

one bus write cycle to setup the command

–

4 bus write cycles to input the source page

address

–

one bus write cycle to issue the confirm

command code

2.

When the device returns to the ready state

(Ready/Busy High), the next bus write cycle of

the command is given with the 4 bus cycles to

input the target page address. Refer to Table

11. for the addresses that must be the same

for the Source and Target pages.

3.

Then the confirm command is issued to start

the P/E/R Controller.

The Data Input cycle for modifying the source

page is performed as shown in Figure 14. After a

Copy Back Program operation, a partial-page pro-

gram is not allowed in the target page until the

block has been erased.

See Figure 14. for an example of the Copy Back

Program operation.

A data input cycle to modify a portion or a multiple

distant portion of the source page, is shown in Fig-

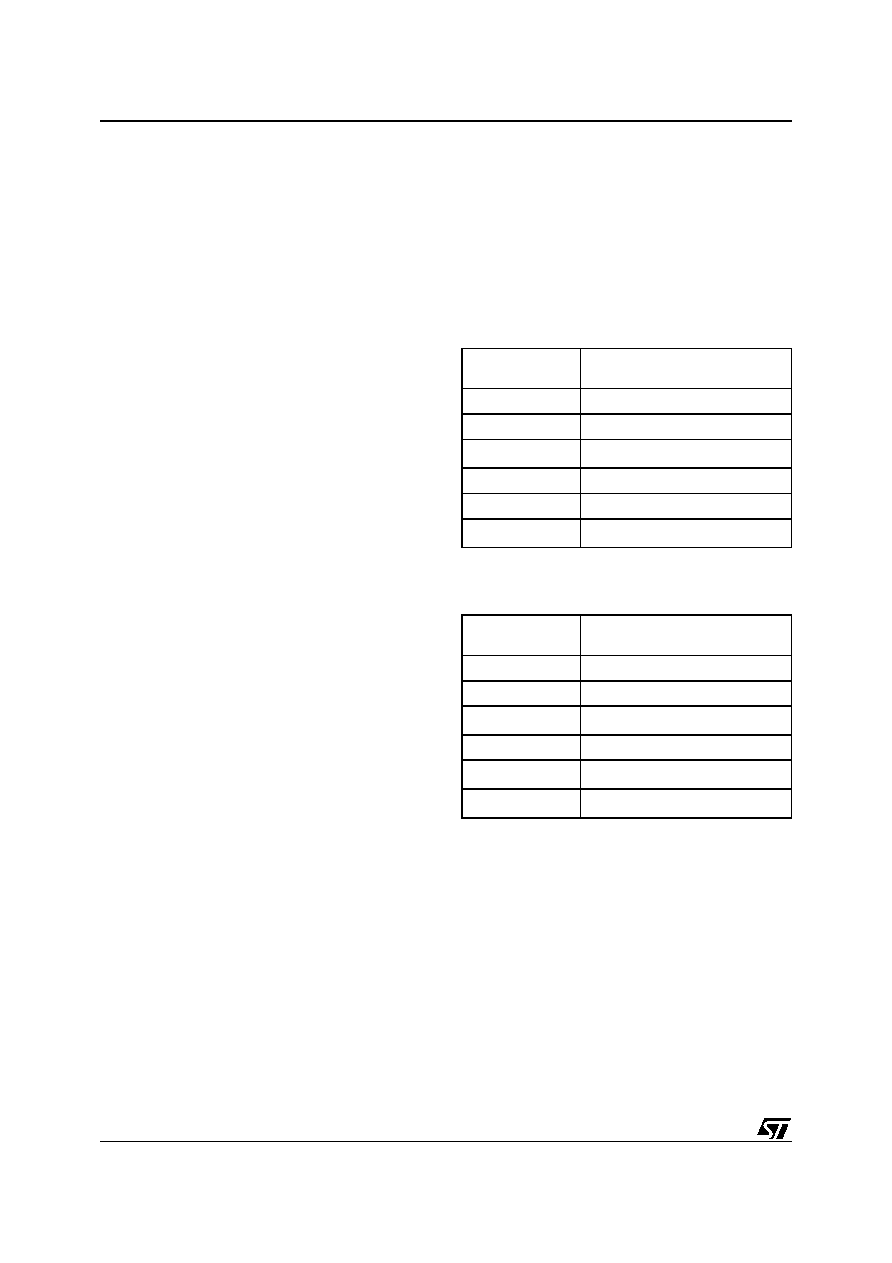

Table 11. Copy Back Program x8 Addresses

Note: 1. DD = Dual Die, QD = Quadruple Die.

Table 12. Copy Back Program x16 Addresses

Note: 1. DD = Dual Die, QD = Quadruple Die.

Density

Same Address for Source and

Target Pages

512 Mbit

no constraint

1 Gbit

no constraint

2 Gbit DD(1)

A28

2 Gbit

no constraint

4 Gbit DD

A29

8 Gbit QD(1)

A29,A30

Density

Same Address for Source and

Target Pages

512 Mbit

no constraint

1 Gbit

no constraint

2 Gbit DD(1)

A27

2 Gbit

no constraint

4 Gbit DD(1)

A28

8 Gbit QD(1)

A28,A29

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NAND08GR4B2BZC6T | 512M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND08GR4B3BN1 | 512M X 16 FLASH 1.8V PROM, 35 ns, PDSO48 |

| NAND512R3B3BZA6E | 64M X 8 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND512W3B3BN6E | 64M X 8 FLASH 3V PROM, 35 ns, PDSO48 |

| NAND512W3B3BZA6E | 64M X 8 FLASH 3V PROM, 35 ns, PBGA63 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| NAND01GW4BZA6 | 制造商:Micron Technology Inc 功能描述:1G, 3V, NAND, VFBGA63, IND - Trays |

| NAND01GW4M0AZB5E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

| NAND01GW4M0AZB5F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

| NAND01GW4M0AZC5E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

| NAND01GW4M0AZC5F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/512Mb/1Gb (x8/x16, 1.8/3V, 528 Byte Page) NAND Flash Memories + 256/512Mb (x16/x32, 1.8V) LPSDRAM, MCP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。