- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382355 > MX812DW (Electronic Theatre Controls, Inc.) VSR CODEC WITH DRAM CONTROL PDF資料下載

參數(shù)資料

| 型號: | MX812DW |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | Codec |

| 英文描述: | VSR CODEC WITH DRAM CONTROL |

| 中文描述: | 振動時效編解碼器DRAM的控制 |

| 文件頁數(shù): | 7/13頁 |

| 文件大小: | 115K |

| 代理商: | MX812DW |

VSR CODEC with DRAM CONTROL

7

MX812 PRELIMINARY INFORMATION

1997 MX

COM Inc.

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA

www.mxcom.com Tele: 800 638-5577 910 744-5050 Fax: 910 744-5054

Doc. # 20480076.003

All trademarks and service marks are held by their respective companies.

The Controlling System ......

“Read Status Register”

– A/C 61

H

, followed by 1 byte of Reply Data.

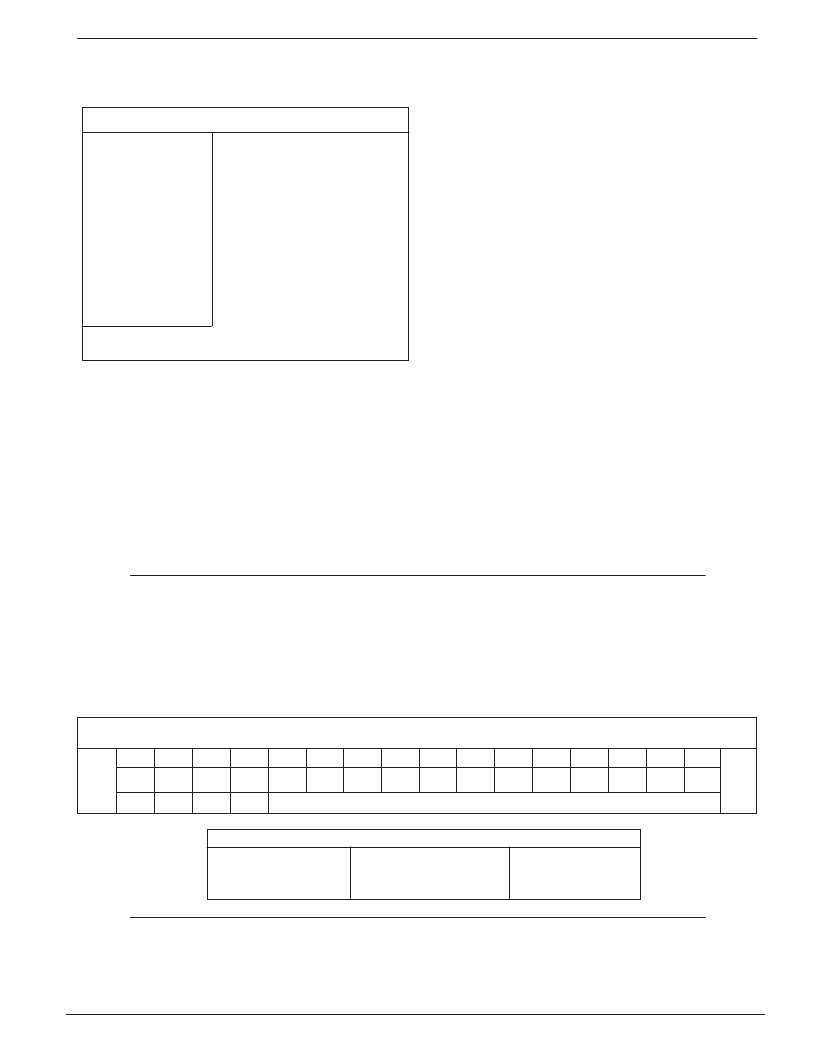

Status Bits

Received from 812 First

Interrupt Condition (Flag)

Bit 6 or 5 set to a “1”

Cleared condition

Command Buffer

Buffer Empty

Cleared condition

Device Condition

Idle

Storing, Playing or Waiting

Input Power Level

Reading

MSB

7

1

0

6

1

0

5

1

0

4

3

2

1

0

Table 3 Status Register

Interrupt Condition (Flag) – IF

Set

to a logic “1” whenever Bit 6 or Bit 5 goes from “0” to

“1” (unless the transition is caused by a General Reset

command 01

). This indication allows monitoring by ‘poll’

while Interrupts are disabled.

Cleared

to a logic “0” by a General Reset command or

immediately following a read of the Status Register.

Command Buffer Status – MT

Set

to a logic “1” when the Command Buffer is empty or

by a General Reset command.

Cleared

to a logic “0” by loading a new Store, Play, Wait

commands.

Device Condition – I

Set

to a logic “1” when

NO

Store, Play or Wait command

is being executed or by a General Reset command.

Set

to a logic “0” while a Store, Play or Wait command is

being executed.

Encode Input Power Level – POWER

Available in the Encode mode, a 5-bit representation of

the analog signal input level, updated at the end of every

Store or Wait command.

This permits the MX812 to perform a continuous sequence

of Store, Play or Wait commands, without gaps and without

requiring an unduly fast response from the mController.

Note that this Command Buffer can only hold one Store,

Play or Wait instruction, each new command received into this

buffer will overwrite any previously loaded contents.

To Store or Play a sequence of pages the relevant commands

should be loaded with sequential page numbers while observing

the Status Register – Bit 6.

Store/Play/Wait Command Buffer

A buffer used to accept and hold the latest Store, Play or

Wait command received over the C-BUS while the MX812 is

executing the previous command. The Status Register, bit 6,

indicates the condition of this buffer.

When a command is received it is first loaded into this

buffer. If the MX812 is already executing a previously loaded

Store, Play or Wait command the new command will be stored

temporarily in the Command Buffer, from where it will be taken

on completion of the previous command.

For the purposes of storage and replay, the attatched

DRAM is divided into ‘data-pages’ of 1024 bits (1kbit).

One Store/Play command (loaded MSB first) will instruct

the MX812 to store or play (depending upon the setting of the

Mode Register, Bit-3) to or from 1 x 1024 “page” of DRAM.

The Store/Play/Wait command buffer will allow continuity of

“Store/Play Page”

– A/C 62

H

, followed by 2 bytes of Command Data.

operation.

The particular page selected is identified by the 12 lowest

bits of the 2 x Store/Play bytes as shown below.

If a Store command is loaded and executed whilst the

Codec is “Powersaved” in the Encode mode, the selected

DRAM page will be filled with an idle pattern (“101010.....”).

“Wait”

– A/C 63

H

, –– Wait for 1024 bit periods

Causes the MX812 to wait for 1024 bit periods (approximately

16 or 32ms).

If the Codec is set to the Encode mode, a new “Power”

reading that is relevant to the input audio level, will be loaded

into the Status Register at the end of the Wait period.

If the Codec is set to the Decode mode it will ‘Play’ a perfect

idle pattern (“101010..........”) during the Wait period.

DRAM Size

4Mbit

1 + 1Mbit

1Mbit

Valid Page Nos

0 – 4095

0 – 2047

0 – 1023

Bit Nos

0 – 11

0 – 10

0 – 9

Bit Number

MSB – Loaded to MX812 First

15

14

13

Loaded Last – LSB

2

Bit

12

11

10

9

8

7

6

5

4

3

1

0

Bit

Value

x

x

x

x

2

11

2

10

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

Value

Page

“0”

“0”

“0”

“0”

––––––––––––––––––––––– DRAM Page Number –––––––––––––––––––––––

Page

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MX812J | VSR CODEC WITH DRAM CONTROL |

| MX841 | White LED Step-Up Converter |

| MX88L284AEC | Highly integration chip for Flat Panel Display application |

| MXA2500U | Ultra Low Noise, 1g Dual Axis Accelerometer with Analog Outputs |

| MXA28A | MOLDED TSSOP JEDEC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MX812J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:VSR CODEC WITH DRAM CONTROL |

| MX-818 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:HIGH SPEED CMOS PROGRAMMABLE ANALOG MULTIPLEXERS |

| MX-818C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:HIGH SPEED CMOS PROGRAMMABLE ANALOG MULTIPLEXERS |

| MX821 | 制造商:Applied Research Technology 功能描述:Rack Mount Eight Channel Mixer with Equalizer 制造商:APPLIED RESEARCH TECHNOLOGY 功能描述:MIXER EIGHT CHANNEL WITH EQ AND DIRECT OUTS |

| MX8217PC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。