- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359234 > MT9043 (Zarlink Semiconductor Inc.) T1/E1 System Synchronizer PDF資料下載

參數(shù)資料

| 型號(hào): | MT9043 |

| 廠(chǎng)商: | Zarlink Semiconductor Inc. |

| 英文描述: | T1/E1 System Synchronizer |

| 中文描述: | T1/E1的系統(tǒng)同步 |

| 文件頁(yè)數(shù): | 7/29頁(yè) |

| 文件大小: | 453K |

| 代理商: | MT9043 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

MT9043

Data Sheet

7

Zarlink Semiconductor Inc.

Lock Indicator - If the PLL is in frequency lock (frequency lock means the center frequency of the PLL is identical to

the line frequency), and the input phase offset is small enough such that no phase slope limiting is exhibited, then

the lock signal will be set high. For specific Lock Indicator design recommendations see the Applications - Lock

Indicator section.

Output Interface Circuit

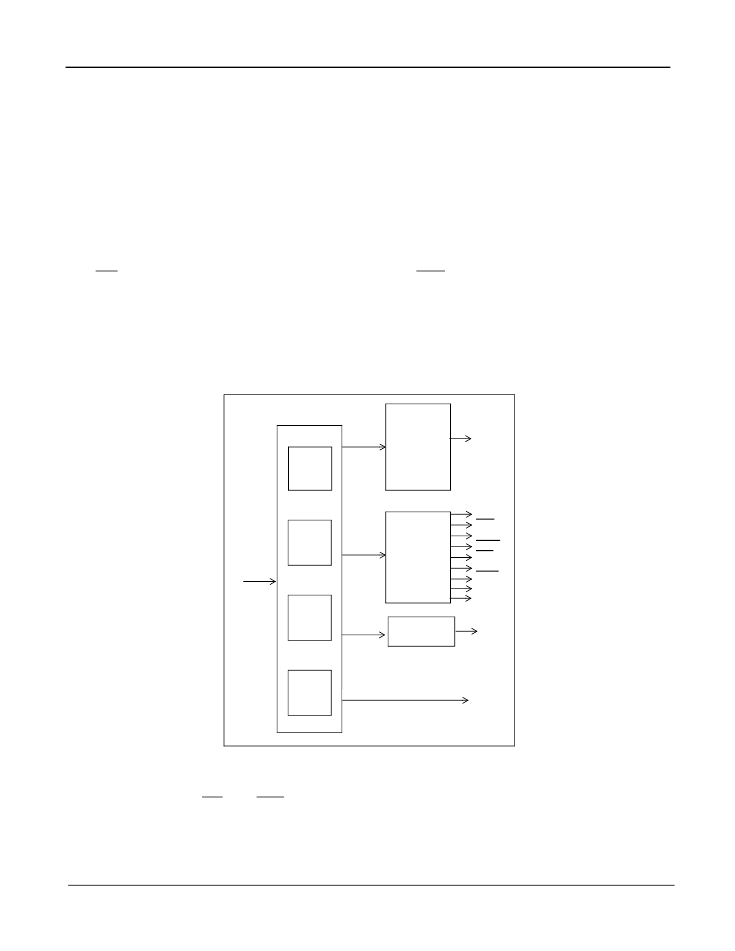

The output of the DCO (DPLL) is used by the Output Interface Circuit to provide the output signals shown in Figure

5. The Output Interface Circuit uses four Tapped Delay Lines followed by a T1 Divider Circuit, an E1 Divider Circuit,

and a DS2 Divider Circuit to generate the required output signals.

Four tapped delay lines are used to generate 16.384MHz, 12.352MHz, 12.624MHz and 19.44 MHz signals.

The E1 Divider Circuit uses the 16.384MHz signal to generate four clock outputs and five frame pulse outputs. The

C8o, C4o and C2o clocks are generated by simply dividing the C16o clock by two, four and eight respectively.

These outputs have a nominal 50% duty cycle.

The T1 Divider Circuit uses the 12.384MHz signal to generate the C1.5o clock by dividing the internal C12 clock

by eight. This output has a nominal 50% duty cycle.

The DS2 Divider Circuit uses the 12.624 MHz signal to generate the clock output C6o. This output has a nominal

50% duty cycle.

Figure 5 - Output Interface Circuit Block Diagram

The frame pulse outputs (F0o, F8o, F16o, TSP, and RSP) are generated directly from the C16 clock.

The T1 and E1 signals are generated from a common DPLL signal. Consequently, all frame pulse and clock outputs

are locked to one another for all operating states, and are also locked to the selected input reference in Normal

Mode. See Figures 14 & 15.

Tapped

Delay

Line

From

DPLL

T1 Divider

E1 Divider

16MHz

12MHz

C1.5o

C2o

C4o

C8o

C16o

F0o

F8o

F16o

RSP

TSP

Tapped

Delay

Line

Tapped

Delay

Line

Tapped

Delay

Line

DS2 Divider

12MHz

19MHz

C6o

C19o

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9043AN | T1/E1 System Synchronizer |

| MT9043AN48PINSSOP | T1/E1 System Synchronizer |

| MT9045 | T1/E1/OC3 System Synchronizer |

| MT9045AN | T1/E1/OC3 System Synchronizer |

| MT9046 | T1/E1 System Synchronizer with Holdover |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9043AN | 制造商:Microsemi Corporation 功能描述: |

| MT9043AN1 | 制造商:Microsemi Corporation 功能描述:PB FREE T1/E1 SYSTEM SYNCHRONIZER 制造商:Microsemi Corporation 功能描述:FRAMER E1/T1 3.3V 48SSOP - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER T1/E1 48SSOP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER T1/E1 48SSOP |

| MT9043AN48PINSSOP | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:T1/E1 System Synchronizer |

| MT9043ANR1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 3.3V 48SSOP - Tape and Reel 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER T1/E1 48SSOP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER T1/E1 48SSOP |

| MT9044 | 制造商:MITEL 制造商全稱(chēng):Mitel Networks Corporation 功能描述:T1/E1/OC3 System Synchronizer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。