- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383643 > MT8940AE (Mitel Networks Corporation) ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL PDF資料下載

參數(shù)資料

| 型號(hào): | MT8940AE |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

| 中文描述: | 異意法半導(dǎo)體的CMOS總線⑩家庭T1/CEPT數(shù)字集群鎖相環(huán) |

| 文件頁數(shù): | 2/16頁 |

| 文件大小: | 299K |

| 代理商: | MT8940AE |

MT8940

ISO-CMOS

3-28

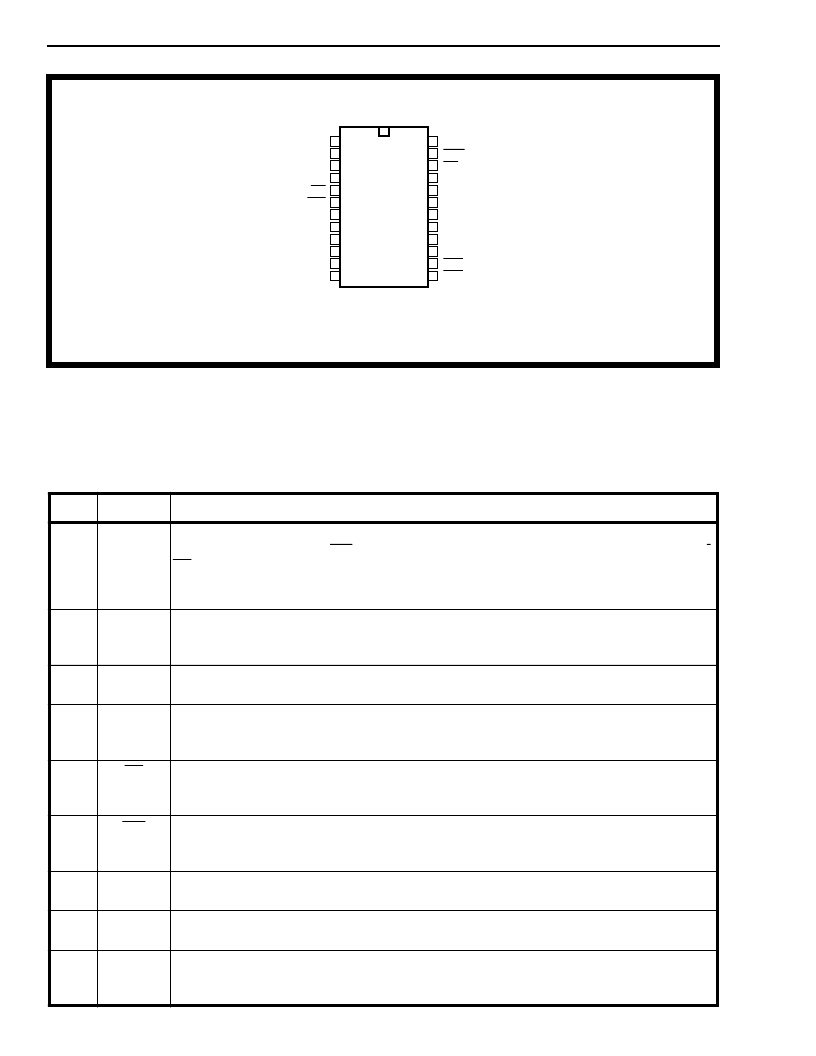

Figure 2 - Pin Connections

Pin Description

Pin #

Name

Description

1

EN

CV

Variable clock enable (TTL compatible input)

- This input (pulled internally to V

DD

) directly

controls the three states of CV (pin 22) under all modes of operation. When HIGH, enables

CV and when LOW, puts it in high impedance condition. It also controls the three states of

CVb signal (pin 21) if MS1 is LOW. When EN

CV

is HIGH, the pin CVb is an output and when

LOW, it is in high impedance state. However, if MS1 is HIGH, CVb is always an input.

2

MS0

Mode select ‘0’ input (TTL compatible) -

This input (pulled internally to V

SS

) in conjunction

with MS1 (pin 4) selects the major mode of operation for both DPLLs. (Refer to Tables 1 and

2).

3

C12i

Clock 12.355 MHz input (TTL compatible) -

Master clock input at 12.355 MHz

±

100ppm for

DPLL #1.

4

MS1

Mode select-1 input (TTL compatible) -

This input (pulled internally to V

SS

) in conjunction

with MS0 (pin 2) selects the major mode of operation for both DPLLs. (Refer to Tables 1 and

2)

5

F0i

Frame pulse input (TTL compatible) -

This is the frame pulse input (pulled internally to

V

DD

) at 8 kHz. The DPLL #1 locks to the falling edge of this input to generate T1 (1.544

MHz) clock.

6

F0b

Frame pulse Bidirectional (TTL compatible input and Totem-pole output) -

Depending

on the minor mode selected for the DPLL #2, it provides the 8 kHz frame pulse output or acts

as an input (pulled internally to V

DD

) to an external frame pulse.

Mode select-2 input (TTL compatible) -

This input (pulled internally to V

DD

) in conjunction

with MS3 (pin 17) selects the minor mode of operation for the DPLL #2. (Refer to Table 3.)

7

MS2

8

C16i

Clock 16.388 MHz input (TTL compatible) -

Master clock input at 16.388 MHz

±

32 ppm for

DPLL #2.

9

EN

C4o

Enable 4.096 MHz clock (TTL compatible input)

- This active high input (pulled internally

to V

DD

) enables C4o (pin 11) output. When LOW, the output C4o is in high impedance

condition.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

24

23

22

21

20

19

18

17

ENVC

MS0

C12i

MS1

F0i

F0b

MS2

C16i

ENC4o

C8Kb

C4o

VSS

VDD

RST

CV

CVb

Yo

Bi

Ai

MS3

ENC2o

C2o

C2o

C4b

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8941B | Advanced T1/CEPT Digital Trunk PLL(先進(jìn)的T1/CEPT數(shù)字中繼鎖相環(huán)) |

| MT8941B | CMOS ST-BUS⑩ FAMILY Advanced T1/CEPT Digital Trunk PLL |

| MT8941BE | CMOS ST-BUS⑩ FAMILY Advanced T1/CEPT Digital Trunk PLL |

| MT8941BP | CMOS ST-BUS⑩ FAMILY Advanced T1/CEPT Digital Trunk PLL |

| MT8950 | ISO-CMOS ST-BUS⑩ FAMILY Data Codec |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8941 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Advanced T1/CEPT Digital Trunk PLL |

| MT8941AE | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Advanced T1/CEPT Digital Trunk PLL |

| MT8941AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Advanced T1/CEPT Digital Trunk PLL |

| MT8941B | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Advanced T1/CEPT Digital Trunk PLL |

| MT8941BE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Advanced T1/CEPT Digital Trunk PLL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。