- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383642 > MT8931C (Mitel Networks Corporation) Subscriber Network Interface Circuit(用戶網(wǎng)絡(luò)接口電路(提供點(diǎn)到點(diǎn)或點(diǎn)到多點(diǎn)數(shù)字傳送)) PDF資料下載

參數(shù)資料

| 型號: | MT8931C |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Subscriber Network Interface Circuit(用戶網(wǎng)絡(luò)接口電路(提供點(diǎn)到點(diǎn)或點(diǎn)到多點(diǎn)數(shù)字傳送)) |

| 中文描述: | 用戶網(wǎng)絡(luò)接口電路(用戶網(wǎng)絡(luò)接口電路(提供點(diǎn)到點(diǎn)或點(diǎn)到多點(diǎn)數(shù)字傳送)) |

| 文件頁數(shù): | 11/40頁 |

| 文件大小: | 309K |

| 代理商: | MT8931C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

MT8931C

9-81

situation is when the system is trying to synchronize

two nodes of a synchronous network. This allows

multiple TEs to share a common ST-BUS timebase.

The synchronization of the loops is established by

using the clock signals produced by a local TE as an

input timing source to the NT slave.

Adaptive Timing Operation

On power-up or after a reset, the SNIC in NT mode is

set to operate in fixed timing. To switch to adaptive

timing, the user should:

1) set the DR bit to 1

2) set the Timing bit to 1 in the C-channel

Control Register

3) wait for 100 ms period

4) proceed in using the AR and DR bits as

desired

Switching from adaptive timing mode is completed

by resetting the Timing bit.

ST-BUS Interface

The ST-BUS is a synchronous time division

multiplexed serial bussing scheme with data streams

operating at 2048 kbit/s configured as 32, 64 kbit/s

channels (refer to Fig. 11). Synchroni-zation of the

data transfer is provided from a frame pulse which

identifies the frame boundaries and repeats at an 8

kHz rate. Figure 4 shows how the frame pulse

(F0b) defines the ST-BUS frame boundaries. All

data is clocked into the device on the rising edge of

the 4096 kHz clock (C4b) three quarters of the way

into the bit cell, while data is clocked out on the

falling edge of the 4096 kHz clock at the start of the

bit cell.

All timing signals (i.e. F0b & C4b) are identified as

bidirectional (denoted by the terminating b). The

I/O configuration of these pins is controlled by the

mode of operation (NT or TE). In the NT mode, all

synchronized signals are supplied from an external

source and the SNIC uses this timing while

transferring information to and from the S or

ST-BUS. In the TE mode, an on-board analog

phase-locked loop extracts timing from the received

data on the S-Bus and generates the system

4096 kHz (C4b) and frame pulse (F0b). The

analog phase-locked loop also maintains proper

phase relation between the timing signals as well as

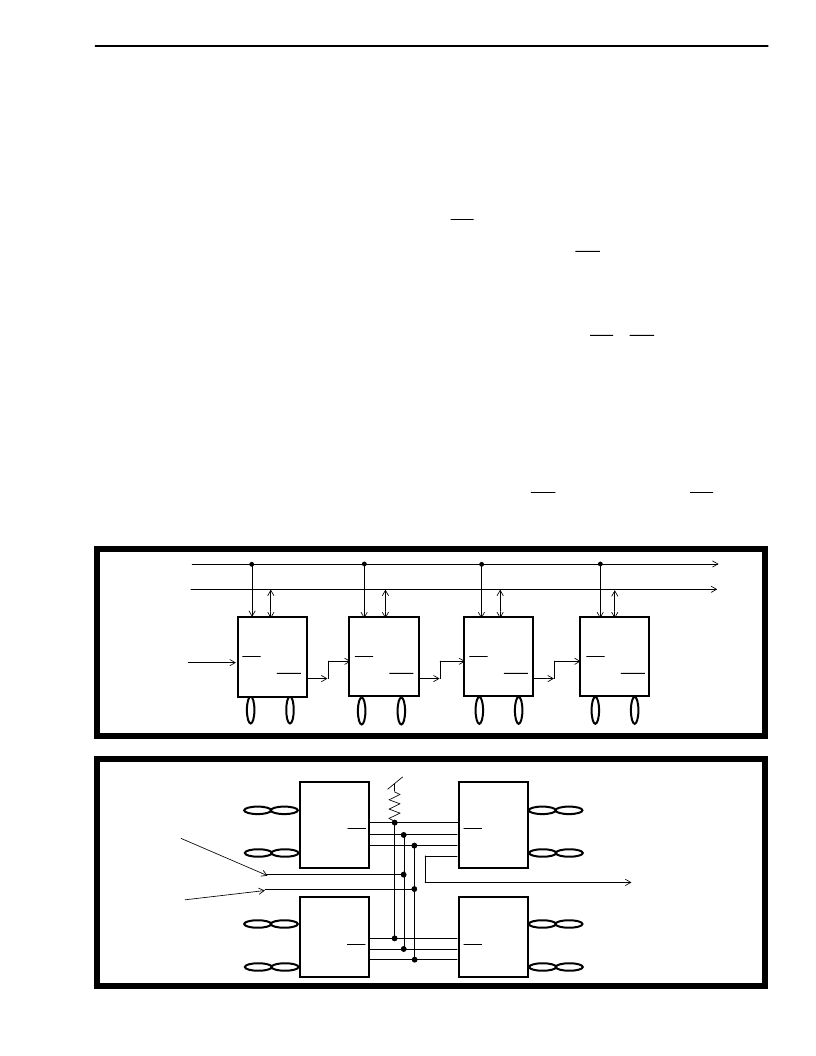

Figure 13 - Daisy Chaining the SNIC

Figure 14 - NT in Star Configuration

ST-BUS Clock

ST-BUS

Stream

System

Frame Pulse

MT8931C

NT

F0b

F0od

MT8931C

NT

F0b

F0od

MT8931C

NT

F0b

F0od

MT8931C

NT

F0b

F0od

to TE

to TE

to TE

to TE

Active on

Channel 0 - 3

Active on

Channels 4 - 7

Active on

Channels 8 - 11

Active on

Channels 12 - 15

V

DD

to TE

to TE

STAR

F0b

DSTi

STAR

F0b

DSTi

MT8931C

NT

MT8931C

NT

MT8931C

NT

MT8931C

NT

to TE

to TE

System

Frame Pulse

Input

ST-BUS Stream

Output

ST-BUS Stream

STAR

F0b

DSTi

DSTo

STAR

F0b

DSTi

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8940 | T1/CEPT Digital Trunk PLL(T1/CEPT數(shù)字中繼鎖相環(huán)) |

| MT8940 | ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

| MT8940-1 | ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

| MT8940AC | T1/CEPT Digital Trunk PLL |

| MT8940AE | ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8931C-1 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8931CC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8931CE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8931CP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8940 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。