- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385639 > MT24D836G (Micron Technology, Inc.) 8Meg x 36 Parity DRAM SIMMs(8M x 36奇偶校驗(yàn)動(dòng)態(tài)RAM(單列直插存儲(chǔ)器模塊)) PDF資料下載

參數(shù)資料

| 型號(hào): | MT24D836G |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | 8Meg x 36 Parity DRAM SIMMs(8M x 36奇偶校驗(yàn)動(dòng)態(tài)RAM(單列直插存儲(chǔ)器模塊)) |

| 中文描述: | 8Meg × 36平價(jià)的DRAM的SIMM(8米× 36奇偶校驗(yàn)動(dòng)態(tài)隨機(jī)存儲(chǔ)器(單列直插存儲(chǔ)器模塊)) |

| 文件頁(yè)數(shù): | 2/17頁(yè) |

| 文件大小: | 308K |

| 代理商: | MT24D836G |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

4, 8 Meg x 36 Parity DRAM SIMMs

DM45.pm5 – Rev. 3/97

Micron Technology, Inc., reserves the right to change products or specifications without notice.

1997, Micron Technology, Inc.

2

4, 8 MEG x 36

PARITY DRAM SIMMs

OBSOLETE

the RAS# HIGH time. Memory cell data is retained in its

correct state by maintaining power and executing any

RAS# cycle (READ, WRITE) or RAS# refresh cycle (RAS#

ONLY, CBR or HIDDEN) so that all 2,048 combinations of

RAS# addresses (A 0-A10) are executed at least every 32ms,

regardless of sequence. The CBR REFRESH cycle will in-

voke the refresh counter for automatic RAS# addressing.

x18 CONFIGURATION

For x18 applications, the corresponding DQ and CAS#

pins must be connected together (DQ1 to DQ19, DQ2

to DQ20 and so forth, and CAS0# to CAS2# and CAS1# to

CAS3#). Each RAS# is then a bank select for the x18 memory

organization.

FAST PAGE MODE

FAST PAGE MODE operations allow faster data opera-

tions (READ or WRITE) within a row-address-defined (A0-

A10) page boundary. The FAST PAGE MODE cycle is

always initiated with a row address strobed-in by RAS#

followed by a column address strobed-in by CAS#. CAS#

may be toggled-in by holding RAS# LOW and strobing-in

different column addresses, thus executing faster memory

cycles. Returning RAS# HIGH terminates the FAST PAGE

MODE operation.

REFRESH

Returning RAS# and CAS# HIGH terminates a memory

cycle and decreases chip current to a reduced standby level.

Also, the chip is preconditioned for the next cycle during

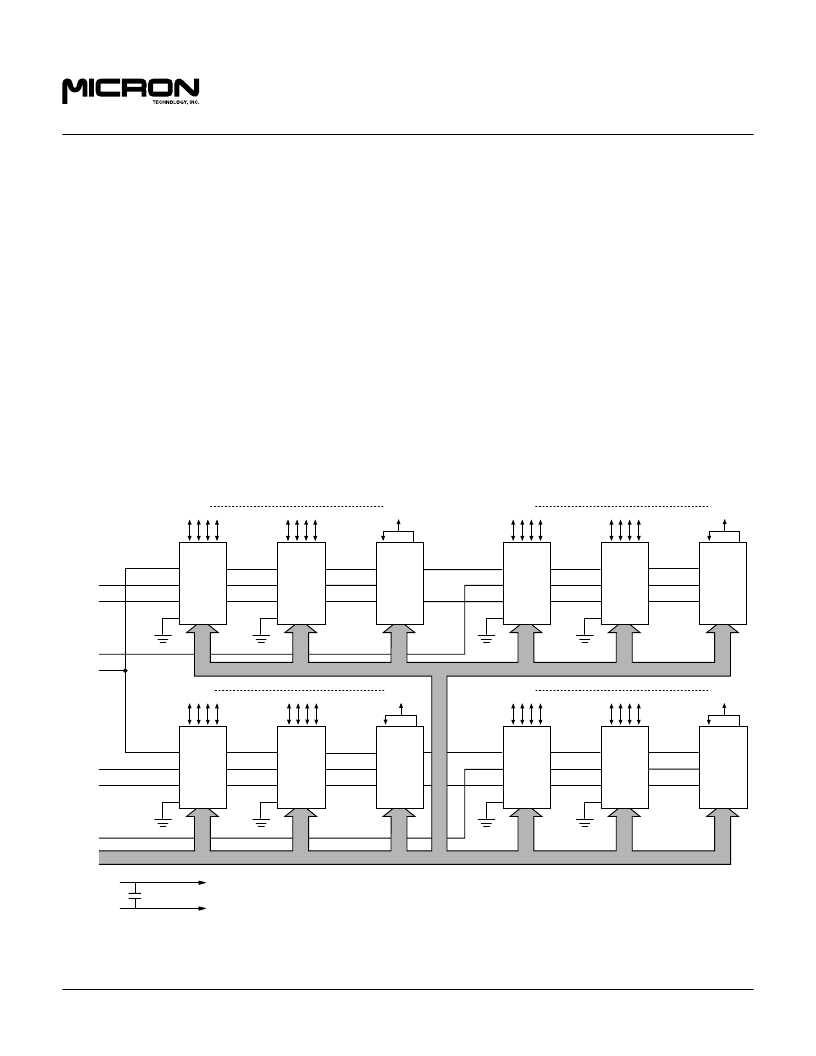

FUNCTIONAL BLOCK DIAGRAM

MT12D436 (16MB)

DQ1-4

U1

DQ1-4

D

DQ1

DQ1-4

DQ1-4

DQ10

DQ18

CAS1#

WE#

DQ1-4

A0-A10

A0-A10

DQ19

DQ27

DQ1-4

A0-A10

DQ1-4

A0-A10

DQ28

DQ36

CAS3#

A0-A10

11

11

11

11

11

11

11

11

11

U2

U9

U3

U4

U5

U6

U7

U8

U1-U8 = 4 Meg x 4 DRAMs

U9-U12 = 4 Meg x 1 DRAMs

DQ9

D

A0-A10

U10

A0-A10

U12

A0-A10

U11

11

11

11

Q

Q

D

Q

D

Q

DQ1-4

A0-A10

A0-A10

A0-A10

A0-A10

A0-A10

CAS0#

RAS0#

CAS2#

RAS2#

V

CC

V

SS

U1-U12

U1-U12

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

OE#

WE#

CAS#

RAS#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT24D836M | 8Meg x 36 Parity DRAM SIMMs(8M x 36奇偶校驗(yàn)動(dòng)態(tài)RAM(單列直插存儲(chǔ)器模塊)) |

| MT28C3224P20 | FLASH AND SRAM COMBO MEMORY |

| MT28F200B3 | FLASH MEMORY |

| MT28F200B5 | FLASH MEMORY |

| MT28F320A18 | FLASH MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT24D836G-XX | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:DRAM MODULE |

| MT24D836M-XX | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:DRAM MODULE |

| MT24-FB | 制造商:Tamura Corporation of America 功能描述: |

| MT25 | 功能描述:接線端子工具和配件 Markg Tag 25mm Blank (pack of 100) RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Tools & Accessories 類型:End Bracket |

| MT-25 | 制造商:ESSENTRA COMPONENTS 功能描述:STAINLESS STL TIE 7.91"LG 250LB 制造商:Richco 功能描述:STAINLESS STL TIE 7.91"LG 250LB |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。