- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98044 > MSC8152TVT1000B (FREESCALE SEMICONDUCTOR INC) RISC PROCESSOR, PBGA783 PDF資料下載

參數(shù)資料

| 型號(hào): | MSC8152TVT1000B |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RISC PROCESSOR, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCBGA-783 |

| 文件頁(yè)數(shù): | 43/68頁(yè) |

| 文件大小: | 907K |

| 代理商: | MSC8152TVT1000B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)當(dāng)前第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

MSC8152 Dual-Core Digital Signal Processor Data Sheet, Rev. 1

Electrical Characteristics

Freescale Semiconductor

48

2.6.5

Ethernet Timing

This section describes the AC electrical characteristics for the Ethernet interface.

There are programmable delay units (PDU) that should be programmed differently for each interface to meet timing. There is

a general configuration register 4 (GCR4) used to configure the timing. For additional information, see the MSC8152 Reference

Manual.

2.6.5.1

Management Interface Timing

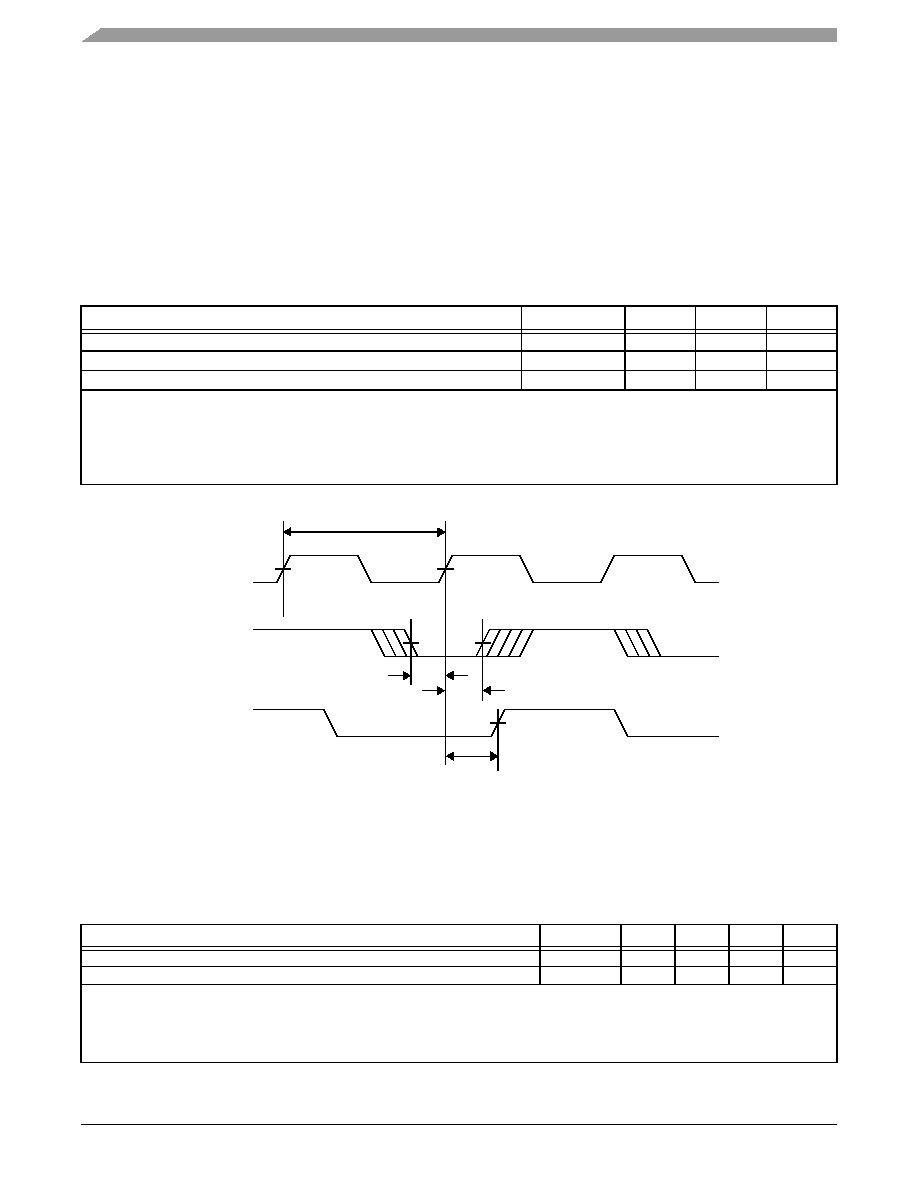

Table 33 lists the timer input Ethernet controller management interface timing specifications shown in Table 24.

2.6.5.2

RGMII AC Timing Specifications

Table 34 presents the RGMII AC timing specifications for applications requiring an on-board delayed clock.

Table 33. Ethernet Controller Management Interface Timing

Characteristics

Symbol

Min

Max

Unit

GE_MDC to GE_MDIO delay2

tMDKHDX

10

70

ns

GE_MDIO to GE_MDC rising edge setup time

tMDDVKH

7—

ns

GE_MDC rising edge to GE_MDIO hold time

tMDDXKH

0—

ns

Notes:

1.

Program the GE_MDC frequency (fMDC) to a maximum value of 2.5 MHz (400 ns period for tMDC). The value depends on the

source clock and configuration of MIIMCFG[MCS] and UPSMR[MDCP]. For example, for a source clock of 400 MHz to

achieve fMDC = 2.5 MHz, program MIIMCFG[MCS] = 0x4 and UPSMR[MDCP] = 0. See the MSC8152 Reference Manual for

configuration details.

2.

The value depends on the source clock. For example, for a source clock of 267 MHz, the delay is 70 ns. For a source clock of

333 MHz, the delay is 58 ns.

Figure 24. MII Management Interface Timing

Table 34. RGMII at 1 GHz2 with On-Board Delay3 AC Timing Specifications

Parameter/Condition

Symbol

Min

Typ

Max

Unit

Data to clock output skew (at transmitter)4

tSKEWT

–-0.5

—

0.5

ns

Data to clock input skew (at receiver) 4

tSKEWR

1—

2.6

ns

Notes:

1.

At recommended operating conditions with VDDIO of 2.5 V ± 5%.

2.

RGMII at 100 MHz support is guaranteed by design.

3.

Program GCR4 as 0x00000000.

4.

This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns and

less than 2.0 ns is added to the associated clock signal.

GE_MDC

GE_MDIO

(Input)

(Output)

tMDC

tMDDXKH

tMDDVKH

tMDKHDX

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8154ETVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8252TVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8252SVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSD1010LT3 | 100 mA, 15 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| MSD1010LT1 | 100 mA, 15 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8154 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Quad-Core Digital Signal Processor |

| MSC8154_11 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Quad-Core Digital Signal processor |

| MSC8154E | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Quad-Core Digital Signal Processor with Security |

| MSC8154E_11 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Quad-Core Digital Signal Processor with Security |

| MSC8154ESVT1000B | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC DSP StarCore 6-cores RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。