- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383639 > MRF24J40 (Microchip Technology Inc.) IEEE 802.15.4⑩ 2.4 GHz RF Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | MRF24J40 |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | IEEE 802.15.4⑩ 2.4 GHz RF Transceiver |

| 中文描述: | IEEE 802.15.4標(biāo)準(zhǔn)⑩2.4 GHz射頻收發(fā)器 |

| 文件頁(yè)數(shù): | 36/66頁(yè) |

| 文件大小: | 748K |

| 代理商: | MRF24J40 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

MRF24J40

DS39776A-page 34

Advance Information

2006 Microchip Technology Inc.

7.4.2

FREEING RECEIVE BUFFER SPACE

The RX buffer is cleared when the length byte of the

packet and the last byte of the FCS are read. Once both

of these values are read from the RX buffer, the buffer

will enable itself to receive another packet. Because

the LQI and RSSI values are appended to the end of

the packet after the FCS, it may be advisable to read

these values out of the RX buffer before reading the

FCS.

Alternatively, it is possible to clear the RX buffer by

flushing it. This is done through the RXFLUSH register.

7.5

Transceiver

The MRF24J40 receiver features a low IF architecture

and consists of an LNA, a pair of down conversion

mixers, polyphase channel filters, baseband limiter

amplifiers and RSSI technology. An ADC is used to

sample the RSSI value and the sampled data is stored

in a register from which the data can be read out via the

SPI bus. The local oscillator generation circuits (VCO,

PLL and buffers) are shared with the receiver and

transmitter. The Low Noise Amplifier (LNA) features a

differential input for high performance. The RX/TX

switch is integrated and LNA input and Power Amplifier

(PA) output share the same pins. A common external

matching network and single-ended to differential con-

version is required. The transmitter features a direct

conversion architecture and has a 0 to -38.75 dBm out-

put power. The output power adjustment is in 1.25 dB

step. The TX gain is programmed by the SPI bus.

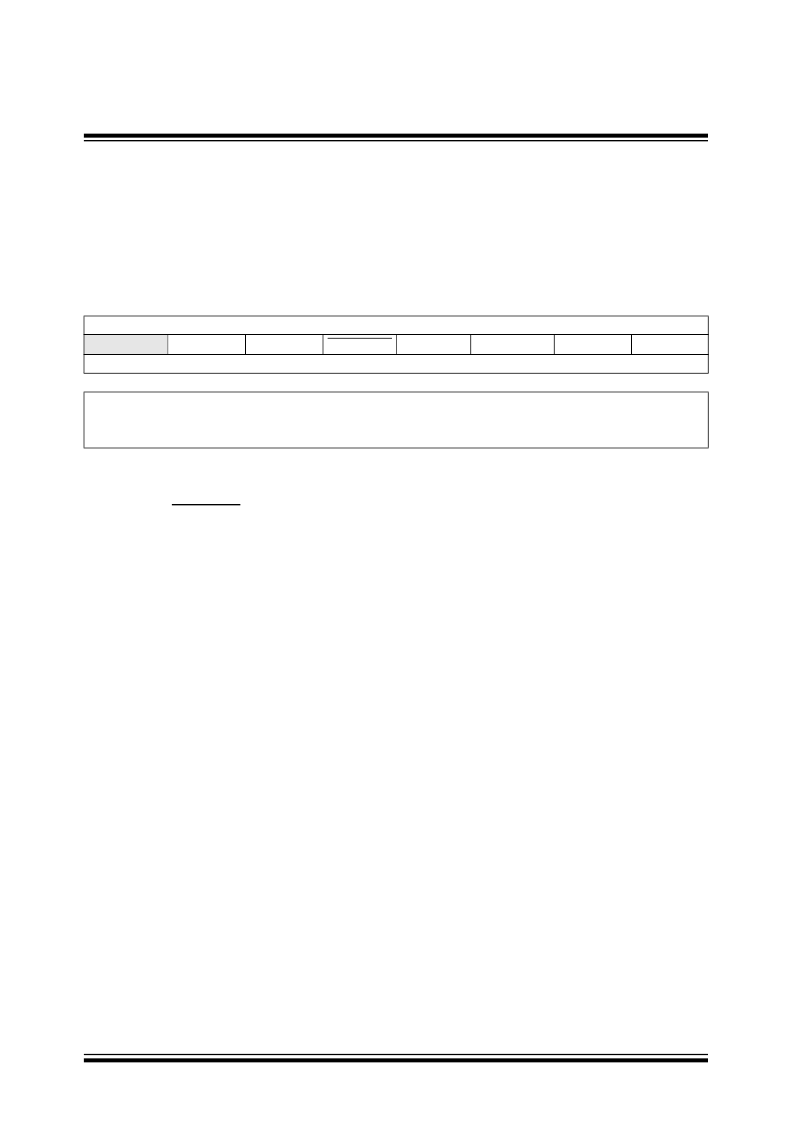

REGISTER 7-3:

RXFLUSH: RECEIVE FIFO FLUSH REGISTER

U-0

—

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

W-0

r

r

RXWRTBLK

CMDONLY

DATAONLY

BCNONLY

RXFLUSH

bit 7

bit 0

Legend:

R = Readable bit

-n = Value at POR

W = Writable bit

‘1’ = Bit is set

U = Unimplemented bit, read as ‘0’

‘0’ = Bit is cleared

x = Bit is unknown

bit 7

bit 6-5

bit 4

Unimplemented:

Read as ‘

0

’

Reserved:

Maintain as ‘

0

’

RXWRTBLK:

Software Write to RX FIFO Address bit

1

= Writing to any RX FIFO address is enabled

0

= Writing to any RX FIFO address is disabled

CMDONLY:

Command Packet Receive bit

1

= Only command packets are received, all other packets are filtered out

0

= All valid packets are received

DATAONLY:

Data Packet Receive bit

1

= Only data packets are received, all other packets are filtered out

0

= All valid packets are received

BCNONLY:

Beacon Packet Receive bit

1

= Only beacon packets are received, all other packets are filtered out

0

= All valid packets are received

RXFLUSH:

Flush RX FIFO Address bit

1

= Flush the RX FIFO. Cleared by hardware.

0

=

Previous flush complete

bit 3

bit 2

bit 1

bit 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MRF24J40-I | IEEE 802.15.4⑩ 2.4 GHz RF Transceiver |

| MRF24J40-IMM | IEEE 802.15.4⑩ 2.4 GHz RF Transceiver |

| MRSM75 | Rotation detection MR sensor |

| MRUS51S | Micro power Built-in IC ultra-minimum MR sensor |

| MS-012AA | SOIC: 8−LEAD (POWER ICS ONLY) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MRF24J40_08 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:IEEE 802.15.4? 2.4 GHz RF Transceiver |

| MRF24J40_10 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:IEEE 802.15.4a?¢ 2.4 GHz RF Transceiver |

| MRF24J40-I | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:IEEE 802.15.4⑩ 2.4 GHz RF Transceiver |

| MRF24J40-I/ML | 功能描述:射頻收發(fā)器 2.4 Ghz IEEE/ZigBee RoHS:否 制造商:Atmel 頻率范圍:2322 MHz to 2527 MHz 最大數(shù)據(jù)速率:2000 Kbps 調(diào)制格式:OQPSK 輸出功率:4 dBm 類型: 工作電源電壓:1.8 V to 3.6 V 最大工作溫度:+ 85 C 接口類型:SPI 封裝 / 箱體:QFN-32 封裝:Tray |

| MRF24J40-I/ML | 制造商:Microchip Technology Inc 功能描述:ZIGBEE Transceiver IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。