- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45354 > MPC8241LZQ266D (MOTOROLA INC) 32-BIT, 266 MHz, RISC PROCESSOR, PBGA357 PDF資料下載

參數(shù)資料

| 型號: | MPC8241LZQ266D |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA357 |

| 封裝: | 25 X 25 MM, 1.27 MM HEIGHT, PLASTIC, BGA-357 |

| 文件頁數(shù): | 42/64頁 |

| 文件大小: | 827K |

| 代理商: | MPC8241LZQ266D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

MOTOROLA

MPC8241 Integrated Processor Hardware Specifications

47

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

System Design Information

7

System Design Information

This section provides electrical and thermal design recommendations for successful application of the

MPC8241.

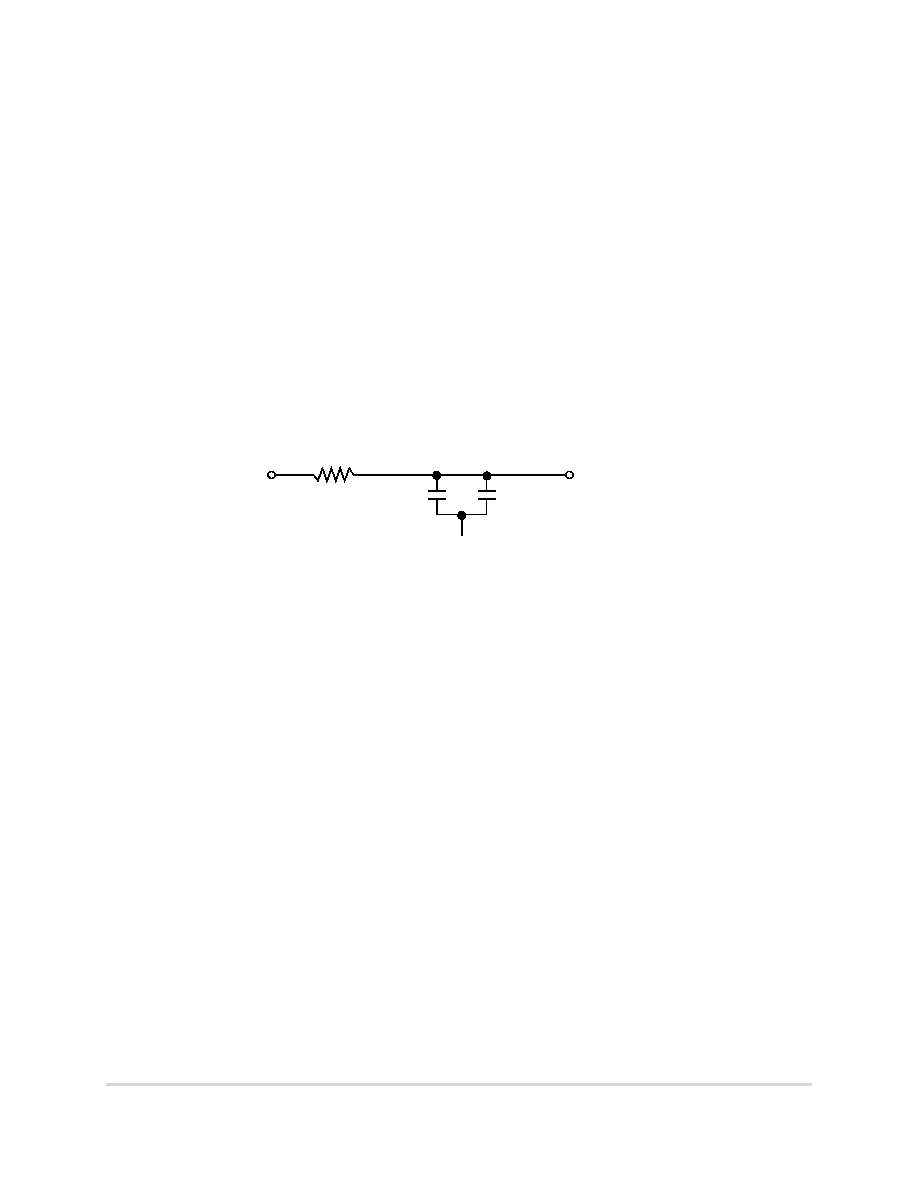

7.1 PLL Power Supply Filtering

The AVDD and AVDD2 power signals on the MPC8241 provide power to the peripheral logic/memory bus

PLL and the MPC603e processor PLL. To ensure stability of the internal clocks, the power supplied to the

AVDD and AVDD2 input signals should be filtered of any noise in the 500 kHz to 10 MHz resonant

frequency range of the PLLs. Motorola recommends two separate circuits that are similar to the one shown

in Figure 28 using surface mount capacitors with minimum effective series inductance (ESL) for AVDD and

AVDD2 power signal pins. In High Speed Digital Design: A Handbook of Black Magic (Prentice Hall, 1993)

Dr. Howard Johnson recommends using multiple small capacitors of equal value instead of multiple values.

Place the circuits as close as possible to the respective input signal pins to minimize noise coupled from

nearby circuits. Routing directly as possible from the capacitors to the input signal pins with minimal

inductance of vias is important.

Figure 28. PLL Power Supply Filter Circuit

7.2 Decoupling Recommendations

Dynamic power management, large address and data buses, and high operating frequencies enable the

MPC8241 to generate transient power surges and high frequency noise in its power supply, especially while

driving large capacitive loads. This noise must be prevented from reaching other components in the

MPC8241 system, and the MPC8241 itself requires a clean, tightly regulated source of power. Motorola

recommends that system designers place at least one decoupling capacitor at each VDD, GVDD_OVDD, and

LVDD pin of the MPC8241, and that these decoupling capacitors receive their power from dedicated power

planes in the PCB to utilize short traces to minimize inductance. These capacitors should have a value of

0.1 F. To minimize lead inductance, use only ceramic SMT (surface mount technology) capacitors,

preferably 0508 or 0603, on which connections are made along the length of the part.

In addition, distribute several bulk storage capacitors around the PCB to feed the VDD, GVDD_OVDD, and

LVDD planes and enable quick recharging of the smaller chip capacitors. These bulk capacitors should have

a low ESR (equivalent series resistance) rating to ensure the necessary quick response time, and should be

connected to the power and ground planes through two vias to minimize inductance. Motorola recommends

using bulk capacitors: 100–330 F (AVX TPS tantalum or Sanyo OSCON).

7.3 Connection Recommendations

To ensure reliable operation, Motorola recommends connecting unused inputs to an appropriate signal level.

Unused active-low inputs should be tied to OVDD. Unused active-high inputs should be connected to GND.

All no connect (NC) signals must remain unconnected.

VDD

AVDD or AVDD2

2.2 F

GND

Low ESL Surface Mount Capacitors

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8241LZP266B | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA357 |

| MPC8241LZQ166B | 32-BIT, 166 MHz, RISC PROCESSOR, PBGA357 |

| MPC8241LZQ266B | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA357 |

| MPC8241LVR200B | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA357 |

| MPC8245ARZU400D | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA352 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8241TVR166D | 功能描述:微處理器 - MPU INTEGRATED HOST PROC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8241TVR200D | 功能描述:微處理器 - MPU INTEGRATED HOST PROC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8241TZP166C | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Intergrated Processor Hardware Specifications |

| MPC8241TZP200C | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Intergrated Processor Hardware Specifications |

| MPC8241TZP266C | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Intergrated Processor Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。