- 您現(xiàn)在的位置:買賣IC網 > PDF目錄371134 > MPC2105SG66 (MOTOROLA INC) 256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms PDF資料下載

參數(shù)資料

| 型號: | MPC2105SG66 |

| 廠商: | MOTOROLA INC |

| 元件分類: | SRAM |

| 英文描述: | 256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| 中文描述: | 64K X 72 CACHE SRAM MODULE, 9 ns, PDMA182 |

| 文件頁數(shù): | 16/24頁 |

| 文件大小: | 228K |

| 代理商: | MPC2105SG66 |

MPC2104

MPC2105

MPC2106

MPC2107

16

MOTOROLA FAST SRAM

TAG RAM

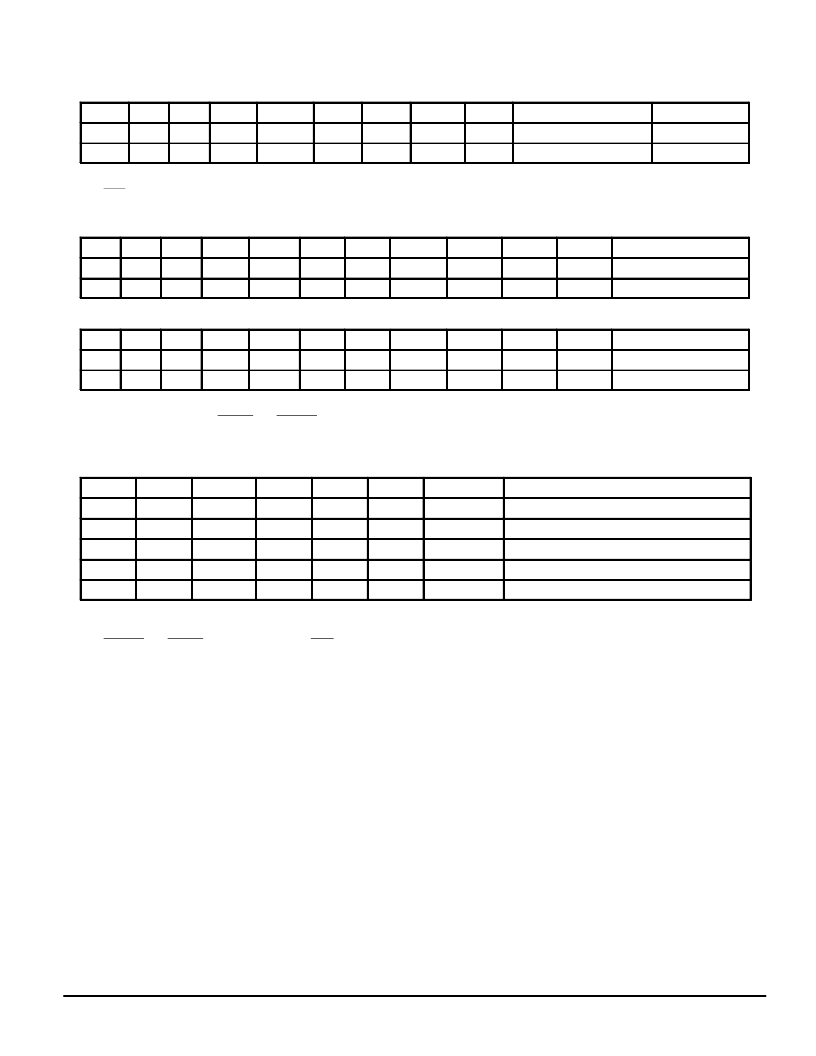

RESET FUNCTION TRUTH TABLE

(See Notes 1 and 2)

TCLR

CLK

TWE

TAG

VLDout

L(3)

DTYout

L(3)

WTout

L(3)

MATCH

L(3)

TA

Operation

POWER

L

L – H

H

High–Z

High–Z

Reset Status

Active

L

L – H

L

—

—

—

—

—

—

Not Allowed

—

NOTES:

1. H = VIH, L = VIL, X = don‘t care, — = unrelated.

2. TOE is X for this table.

READ FUNCTION TRUTH TABLE

(See Notes 1, 2, and 3)

TOE

TWE

CLK

TAG

VLDin

—

DTYin

—

WTin

—

VLDout

—

DTYout

—

WTout

—

MATCH

Operation

L

H

X

DOUT

High–Z

DOUT

—

Read Tag I/O

H

X

X

—

—

—

—

—

—

Tag I/O Disable

WRITE FUNCTION TRUTH TABLE

(See Notes 1 and 2)

TOE

TWE

CLK

TAG

VLDin

—

DTYin

—

WTin

—

VLDout

DOUT

—

DTYout

DOUT

—

WTout

DOUT

—

MATCH

Operation

H

L

L – H

DIN

—

L

Write Tag I/O

L

L

L – H

—

—

—

—

Not Allowed

NOTES:

1. H = VIH, L = VIL, X = don‘t care, — = unrelated.

2. This table applies when RESET and PWRDN are high.

3. DOUT in this case is the same as DIN. The input data is written through to the outputs during the write operation.

MATCH FUNCTION TRUTH TABLE

(See Notes 1 through 4)

TOE

TWE

TAG

VLD(4)

DTY(4)

WT(4)

MATCH

Operation

X

X

—

—

—

—

DOUT

L

Selected

L

H

DOUT

DIN

TAGIN

TAGIN

—

—

—

Read Tag I/O

H

L

DIN

L

DIN

—

DIN

—

L

Write Tag I/O, Status Bits

H

H

L

Invalid Data – Dedicated Status Bits

H

H

H

—

—

M

Match – Dedicated Status Bits

NOTES:

1. H = VIH, L = VIL, X = don‘t care, — = unrelated.

2. M = high if TAGIN equals the memory contents at the address; M = low if TAGIN does not equal the ocntents at that address.

3. PWRDN and RESET are high for this table. OES and CLK are X.

4. This column represents the stored memory cell data for the given status bit at the selected address.

相關PDF資料 |

PDF描述 |

|---|---|

| MPC2105BSG66 | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2605 | Integrated Secondary Cache for PowerPC Microprocessors |

| MPC2605ZP66 | Circular Connector; Body Material:Aluminum; Series:PT07; Number of Contacts:36; Connector Shell Size:22; Connecting Termination:Solder; Circular Shell Style:Jam Nut Receptacle; Circular Contact Gender:Socket |

| MPC2605ZP66R | Integrated Secondary Cache for PowerPC Microprocessors |

| MPC500 | ELECTROHYDRAULIC BRAKING |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC2106ASG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106BSG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106CDG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106SG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2107SG15 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

發(fā)布緊急采購,3分鐘左右您將得到回復。