- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359159 > MDS212 (Zarlink Semiconductor Inc.) 12-Port 10/100Mbps Ethernet Switch PDF資料下載

參數(shù)資料

| 型號(hào): | MDS212 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | 12-Port 10/100Mbps Ethernet Switch |

| 中文描述: | 12端口10/100Mbps以太網(wǎng)交換機(jī) |

| 文件頁(yè)數(shù): | 43/111頁(yè) |

| 文件大小: | 1609K |

| 代理商: | MDS212 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)當(dāng)前第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)

MDS212

Data Sheet

43

Zarlink Semiconductor Inc.

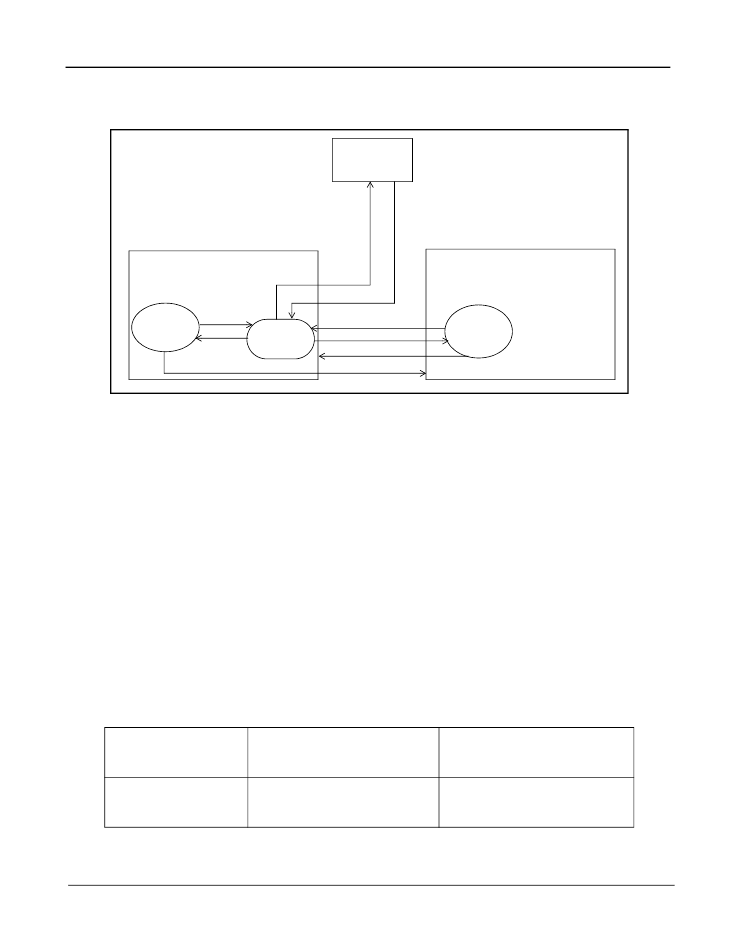

Each device may request access to the CPU Interface by sending a Request signal to the arbiter. The arbiter, then

sends a Grant signal acknowledging which device has been chosen.

Figure 13 - Block Diagram of the Arbiter

Note:

In unmanaged mode, the CPU is used only for debugging purposes and cannot be involved in switching

decisions or management activities.

An arbitrate scheduler, located within the arbiter, decides which device functions as the Master device. If the Master

is the secondary device, the arbiter will send a Grant signal and a Chip Select (P_CS) signal to the device. If the

Master is the primary device, the Grant signal is sent directly to the Master State Machine (MSM) by an internal

signal. The scheduler then performs a round robin configuration and allows each device to be the Master device.

Note:

During Power On/Reset, the arbiter always selects the primary device to be master device.

10.4 CPU Interface In Managed Mode

The CPU Slave State Machine (SSM) accepts Address Strobe (P_ADS#), Chip Select (P_CS#), and Bus- Data

Ready (P_RDY#) signals as ready state signals of a CPU cycle.

10.4.1 CPU Access

The 32-bit CPU bus interface supports both Big and Little Endian CPUs. The difference between Big and Little

Endian is the byte swapping when CPU write data to external memory. Table 7 below summarizes the byte

swapping operation and Figure 14 illustrates an example of bytes swapping.

Table 7 - Little and Big Endian Byte Swapping Operation

If using Little Endian

Bit[1] must be ‘0’ for register of

MWARS, MRARS, MWARB,

MRARB

No byte swapping for CPU data

write in or read out to/from

MWDR, MRDR registers

If using Big Endian

Bit[1] must be ‘1’ for register of

MWARS, MRARS, MWARB,

MRARB

Automatic Byte swapping for CPU

data write in or read out to/from

MWDR, MRDR registers

Only for Debug

CPU

Master the

State

Machine

Arbiter

Chip Select

RBus

Bus Grant

MDS212

Primary

Master the

State

Machine

MDS212

Secondary

P_GNTC

P_REQC

P_REQ1

P_GNT1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MDS212CG | 12-Port 10/100Mbps Ethernet Switch |

| MDS213 | 12-Port 10/100Mbps + 1Gbps Ethernet Switch |

| MDS213CG | 12-Port 10/100Mbps + 1Gbps Ethernet Switch |

| MDS220 | Analog IC |

| MDS221 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MDS212CG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:12-Port 10/100Mbps Ethernet Switch |

| MDS213 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:12-Port 10/100Mbps + 1Gbps Ethernet Switch |

| MDS213CG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:12-Port 10/100Mbps + 1Gbps Ethernet Switch |

| MDS217 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| MDS-21E09 | 制造商:ITT Interconnect Solutions 功能描述:BACKSHELL - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。