- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382321 > MD80C51 (Intel Corp.) CHMOS SINGLE-CHIP 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | MD80C51 |

| 廠商: | Intel Corp. |

| 英文描述: | CHMOS SINGLE-CHIP 8-BIT MICROCONTROLLER |

| 中文描述: | CHMOS單片8位微控制器 |

| 文件頁數(shù): | 10/16頁 |

| 文件大小: | 229K |

| 代理商: | MD80C51 |

AUTOMOTIVE 80C31BH/80C51BH/87C51

EXPLANATION OF THE AC SYMBOLS

Each timing symbol has 5 characters. The first char-

acter is always a ‘T’ (stands for time). The other

characters, depending on their positions, stand for

the name of a signal or the logical status of that

signal. The following is a list of all the characters and

what they stand for.

A:Address.

C:Clock.

D:Input data.

H:Logic level HIGH.

I:Instruction (program memory contents).

L:Logic level LOW, or ALE.

P:PSEN.

Q:Output data.

R:RD signal.

T:Time.

V:Valid.

W:WR signal.

X:No longer a valid logic level.

Z:Float.

For example,

T

AVLL

e

Time from Address Valid to ALE Low.

T

LLPL

e

Time from ALE Low to PSEN Low.

AC CHARACTERISTICS:

(T

A

e b

40

§

C to

a

125

§

C; V

CC

e

5V

g

10% (5V

g

20% EPROM Only);

V

SS

e

0V; Load Capacitance for Port 0, ALE, and PSEN

e

100 pF; Load Capacitance for All Other

Outputs

e

80 pF)

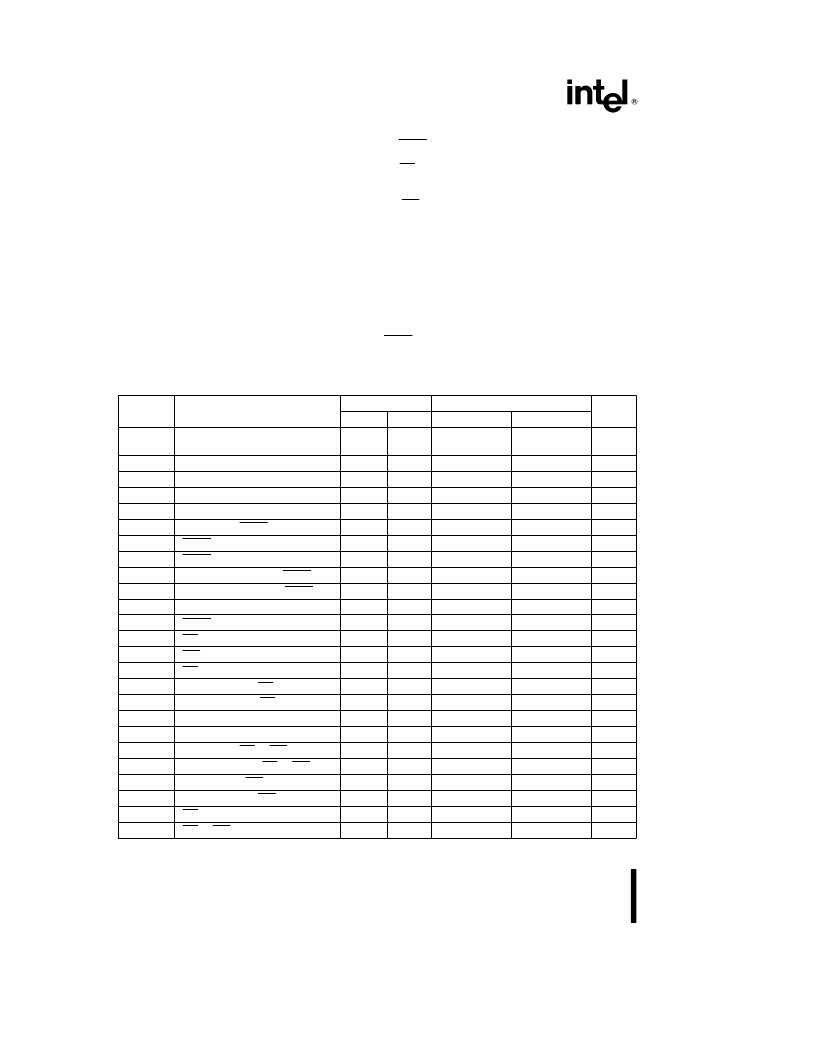

EXTERNAL PROGRAM AND DATA MEMORY CHARACTERISTICS

Symbol

Parameter

12 MHz Osc

Variable Oscillator

Units

Min

Max

Min

Max

1/T

CLCL

Oscillator Frequency

87C51/80C51BH/80C31BH

MHz

3.5

12–16

T

LHLL

T

AVLL

T

LLAX

T

LLIV

T

LLPL

T

PLPH

T

PLIV

T

PXIX

T

PXIZ

T

AVIV

T

PLAZ

T

RLRH

T

WLWH

T

RLDV

T

RHDX

T

RHDZ

T

LLDV

T

AVDV

T

LLWL

T

AVWL

T

QVWX

T

WHQX

T

RLAZ

T

WHLH

ALE Pulse Width

127

2T

CLCL

b

40

T

CLCL

b

55

T

CLCL

b

35

ns

Address Valid to ALE Low

28

ns

Address Hold After ALE Low

48

ns

ALE Low to Valid Instr In

224

4T

CLCL

b

110

ns

ALE Low to PSEN Low

43

T

CLCL

b

40

3T

CLCL

b

45

ns

PSEN Pulse Width

205

ns

PSEN Low to Valid Instr In

135

3T

CLCL

b

115

ns

Input Instr Hold After PSEN

0

0

ns

Input Instr Float After PSEN

59

T

CLCL

b

25

5T

CLCL

b

105

10

ns

Address Valid to Valid Instr In

312

ns

PSEN Low to Address Float

10

ns

RD Pulse Width

400

6T

CLCL

b

100

6T

CLCL

b

100

ns

WR Pulse Width

400

ns

RD Low to Valid Data In

252

5T

CLCL

b

165

ns

Data Hold After RD High

0

0

ns

Data Float After RD High

97

2T

CLCL

b

70

8T

CLCL

b

150

9T

CLCL

b

165

3T

CLCL

a

50

ns

ALE Low to Valid Data In

517

ns

Address Valid to Valid Data In

585

ns

ALE Low to RD or WR Low

200

300

3T

CLCL

b

50

4T

CLCL

b

130

T

CLCL

b

60

T

CLCL

b

50

ns

Address Valid to RD or WR Low

203

ns

Data Valid to WR Transition

23

ns

Data Hold After WR High

33

ns

RD Low to Address Float

0

0

ns

RD or WR High to ALE High

43

123

T

CLCL

b

40

T

CLCL

a

40

ns

10

相關PDF資料 |

PDF描述 |

|---|---|

| MD8284N | Clock Generator and Driver for 8066, 8088 Processors |

| MD8284N-1 | Clock Generator and Driver for 8066, 8088 Processors |

| MD8284N-1B | Clock Generator and Driver for 8066, 8088 Processors |

| MD8284NB | Clock Generator and Driver for 8066, 8088 Processors |

| MD8286 | OCTAL BUS TRANSCEIVER |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MD80C51BH | 制造商:ROCHESTER 制造商全稱:ROCHESTER 功能描述:CMOS SINGLE - CHIP 8-BIT MICROCOMPUTER 64K program Memory Space |

| MD80C51FB | 制造商:Rochester Electronics LLC 功能描述: |

| MD80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C862 | 制造商:Intel 功能描述:PROCESSOR:MICRO-PROCESSOR |

| MD80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復。