- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9324 > MCP4331T-104E/ML (Microchip Technology)IC DGTL POT QUAD 100K 20QFN PDF資料下載

參數(shù)資料

| 型號: | MCP4331T-104E/ML |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 5/35頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DGTL POT QUAD 100K 20QFN |

| 標準包裝: | 3,300 |

| 接片: | 129 |

| 電阻(歐姆): | 100k |

| 電路數(shù): | 4 |

| 溫度系數(shù): | 標準值 150 ppm/°C |

| 存儲器類型: | 易失 |

| 接口: | 4 線 SPI(芯片選擇) |

| 電源電壓: | 1.8 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 125°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 20-VFQFN 裸露焊盤 |

| 供應商設備封裝: | 20-QFN 裸露焊盤(4x4) |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

2010 Microchip Technology Inc.

DS22242A-page 13

MCP433X/435X

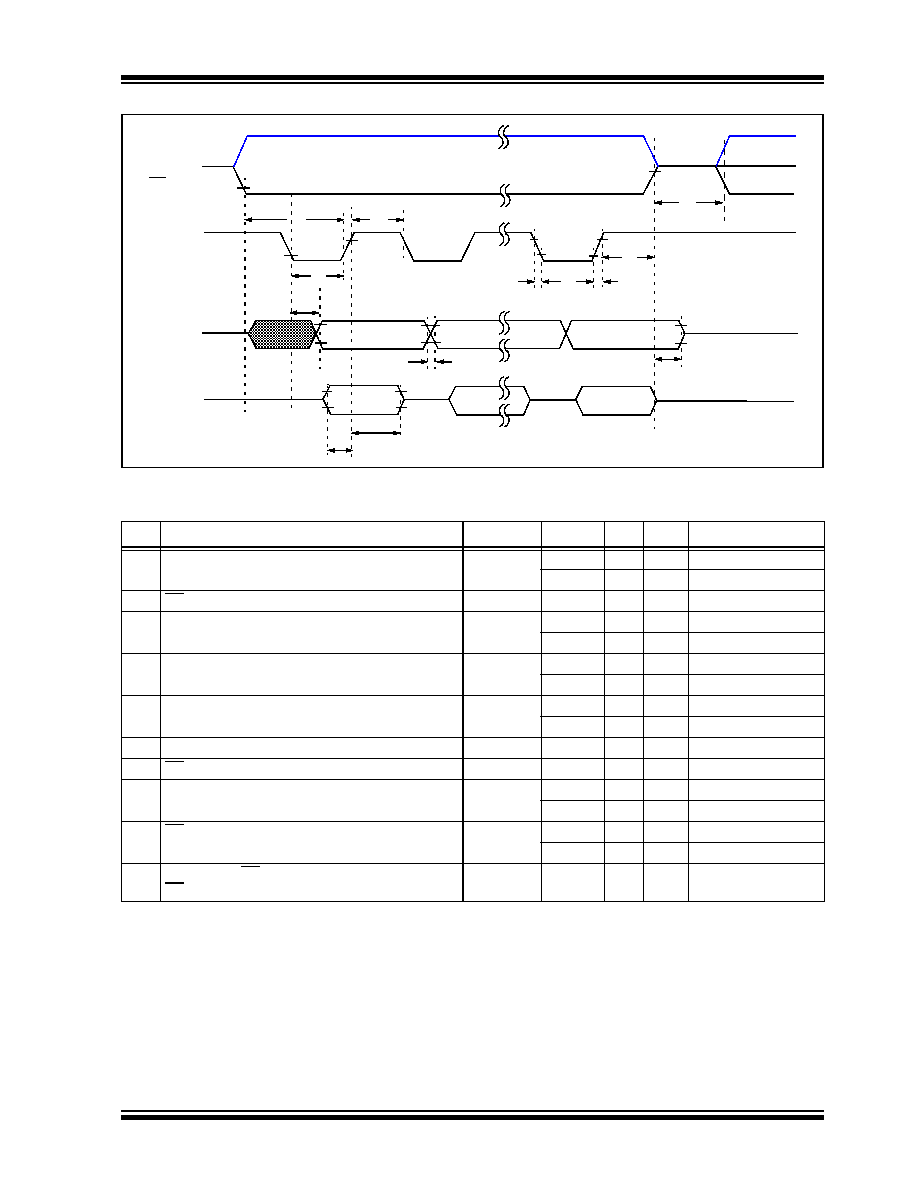

FIGURE 1-2:

SPI Timing Waveform (Mode = 11).

TABLE 1-2:

SPI REQUIREMENTS (MODE = 11)

#

Characteristic

Symbol

Min

Max Units

Conditions

SCK Input Frequency

FSCK

—10

MHz VDD = 2.7V to 5.5V

—1

MHz VDD = 1.8V to 2.7V

70

CS Active (VIL or VIHH) to SCK input

TcsA2scH

60

—

ns

71

SCK input high time

TscH

45

—

ns

VDD = 2.7V to 5.5V

500

—

ns

VDD = 1.8V to 2.7V

72

SCK input low time

TscL

45

—

ns

VDD = 2.7V to 5.5V

500

—

ns

VDD = 1.8V to 2.7V

73

Setup time of SDI input to SCK

edge

TDIV2scH

10

—

ns

VDD = 2.7V to 5.5V

20

—

ns

VDD = 1.8V to 2.7V

74

Hold time of SDI input from SCK

edge

TscH2DIL20

—

ns

77

CS Inactive (VIH) to SDO output high-impedance TcsH2DOZ

—

50

ns

80

SDO data output valid after SCK

edge

TscL2DOV

—

70

ns

VDD = 2.7V to 5.5V

170

ns

VDD = 1.8V to 2.7V

83

CS Inactive (VIH) after SCK edge

TscH2csI

100

—

ns

VDD = 2.7V to 5.5V

1ms

VDD = 1.8V to 2.7V

84

Hold time of CS Inactive (VIH) to

CS Active (VIL or VIHH)

TcsA2csI

50

—

ns

Note 1:

This specification by design.

CS

SCK

SDO

SDI

70

71

72

73

74

75, 76

77

78

79

80

SDI

MSb

LSb

BIT6 - - - - - -1

MSb IN

BIT6 - - - -1

LSb IN

83

84

VIH

VIL

VIHH

VIH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS1744W-120IND | IC RTC RAM Y2K 3.3V 120NS 28EDIP |

| DS1386-8-120 | IC TIMEKEEPER RAM 64K 32-EDIP |

| DS1556P-70 | IC RTC RAM Y2K 5V 70NS 34-PCM |

| DS1315E-33 | IC T-CHIP PHANTOM 3.3V 20-TSSOP |

| DS1315E-5 | IC TIME CHIP PHANTOM 5V 20-TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCP4331T-502E/ML | 功能描述:數(shù)字電位計 IC 5k SPI 7-bit Quad Channel RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4331T-502E/ST | 功能描述:數(shù)字電位計 IC 5k SPI 7-bit Quad Channel RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4331T-503E/ML | 功能描述:數(shù)字電位計 IC 50k SPI 7-bit Quad Channel RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4331T-503E/ST | 功能描述:數(shù)字電位計 IC 50k SPI 7-bit Quad Channel RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4332-103E/ST | 功能描述:數(shù)字電位計 IC 10k SPI Qd Ch 7-Bit Volatile memory RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。