- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45238 > MC68HC11EA9VFN2 (FREESCALE SEMICONDUCTOR INC) 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQCC52 PDF資料下載

參數(shù)資料

| 型號: | MC68HC11EA9VFN2 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQCC52 |

| 封裝: | PLASTIC, LCC-52 |

| 文件頁數(shù): | 19/58頁 |

| 文件大小: | 583K |

| 代理商: | MC68HC11EA9VFN2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

MOTOROLA

MC68HC11EA9

26

MC68HC11EA9TS/D

6 Parallel Input/Output

The MC68HC(7)11EA9 has up to 36 input/output lines, depending on the operating mode. Table 10

shows the configuration and features of each port.

Simple and full handshake input and output functions are available on ports B and C lines in single-chip

mode. The following is a description of the handshake functions.

In simple strobed mode, port B is a strobed output port and port C is a latching input port. The two ac-

tivities are available simultaneously.

The STRB output is pulsed for two E-clock periods each time there is a write to the PORTB register.

The INVB bit in the PIOC register controls the polarity of STRB pulses. Port C levels are latched into

the alternate port C latch (PORTCL) register on each assertion of the STRA input. STRA edge select,

flag, and interrupt enable bits are located in the PIOC register. Any or all of the port C lines can still be

used as general-purpose I/O while in strobed input mode.

Full handshake modes involve port C pins and the STRA and STRB lines. Input and output handshake

modes are supported, and output handshake mode has a three-stated variation. STRA is an edge de-

tecting input, and STRB is a handshake output. Control and enable bits are located in the PIOC register.

In full input handshake mode, the MCU uses STRB as a ready line to an external system. Port C logic

levels are latched into PORTCL when the STRA line is asserted by the external system. The MCU then

negates STRB. The MCU reasserts STRB after the PORTCL register is read. A mix of latched inputs,

static inputs, and static outputs is allowed on port C, differentiated by the data direction bits and use of

the PORTC and PORTCL registers.

In full output handshake mode, the MCU writes data to PORTCL which, in turn, asserts the STRB output

to indicate that data is ready. The external system reads port C and asserts the STRA input to acknowl-

edge that data has been received.

In the three-state variation of output handshake mode, lines intended as three-state handshake outputs

are configured as inputs by clearing the corresponding DDRC bits. The MCU writes data to PORTCL

and asserts STRB. The external system responds by activating the STRA input, which forces the MCU

to drive the data in PORTCL out on all of the port C lines. The mode variation does not allow part of port

C to be used for static inputs while other port C pins are being used for handshake outputs. Refer to

PIOC register description for further information.

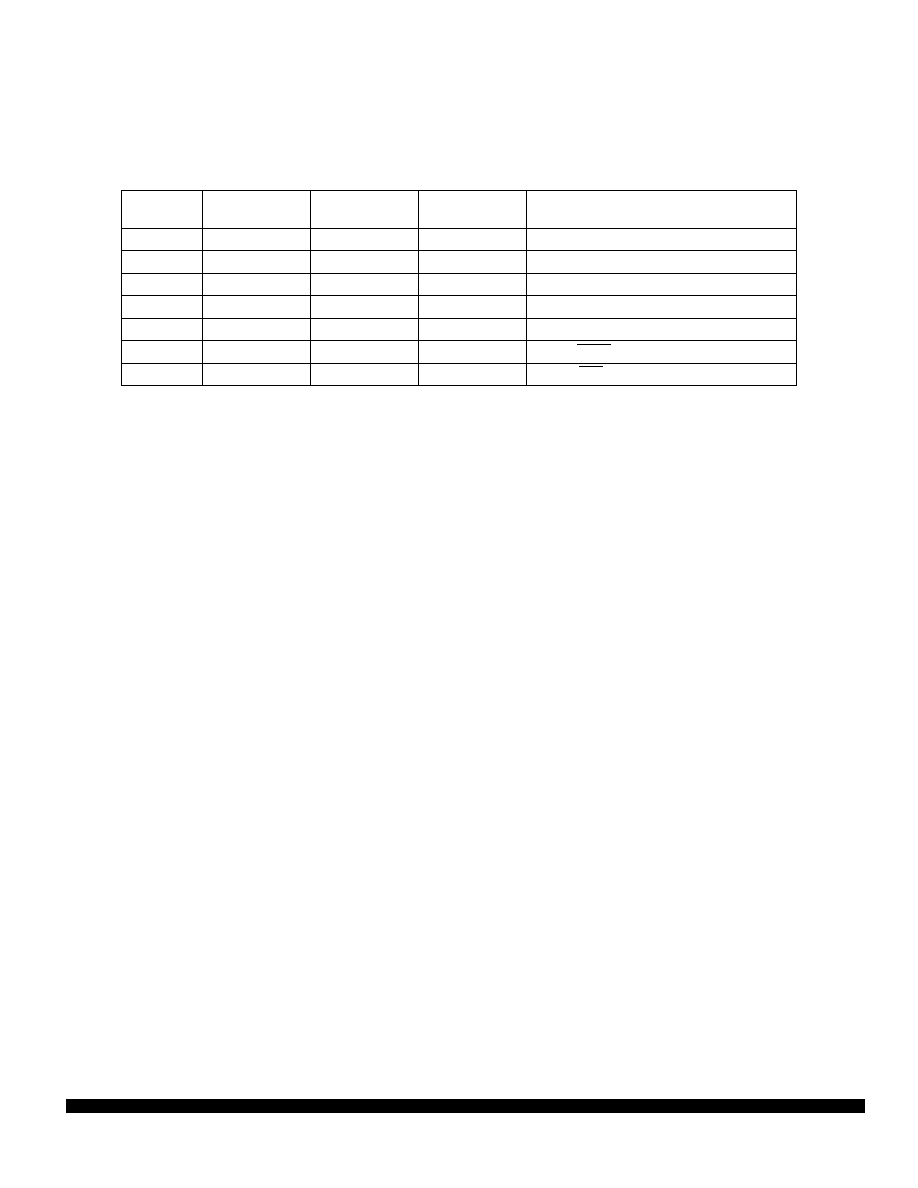

Table 10 I/O Port Configuration

Port

Input

Pins

Output

Pins

Bidirectional

Pins

Shared Functions

A

—

8

Timer

B

—

8

High Order Address

C

—

8

Multiplexed Low Order Address/Data

D

—

2

SCI/PLL Test

E

8

—

A/D Converter

—

1

—

XPIN (XIRQ pin configured for data input)

—

1

—

IPIN (IRQ pin configured for data input)

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC11EA9CFN3 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQCC52 |

| MC68HC11EA9MFN2 | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQCC52 |

| MC68HC711EA9VP3 | 8-BIT, OTPROM, 3 MHz, MICROCONTROLLER, PDIP56 |

| MC68HC711EA9MFS3 | 8-BIT, UVPROM, 3 MHz, MICROCONTROLLER, CQCC52 |

| MC68HC711EA9MP3 | 8-BIT, OTPROM, 3 MHz, MICROCONTROLLER, PDIP56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11EA9VFN3 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontrollers |

| MC68HC11EA9VP2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontrollers |

| MC68HC11EA9VP3 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontrollers |

| MC68HC11ED0 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Technical Summary |

| MC68HC11ED0CFN2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Technical Summary |

發(fā)布緊急采購,3分鐘左右您將得到回復。