采購需求

(若只采購一條型號,填寫一行即可)| *型號 | *數量 | 廠商 | 批號 | 封裝 |

|---|---|---|---|---|

|

|

添加更多采購

| 型號: | MC68302CFC20 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

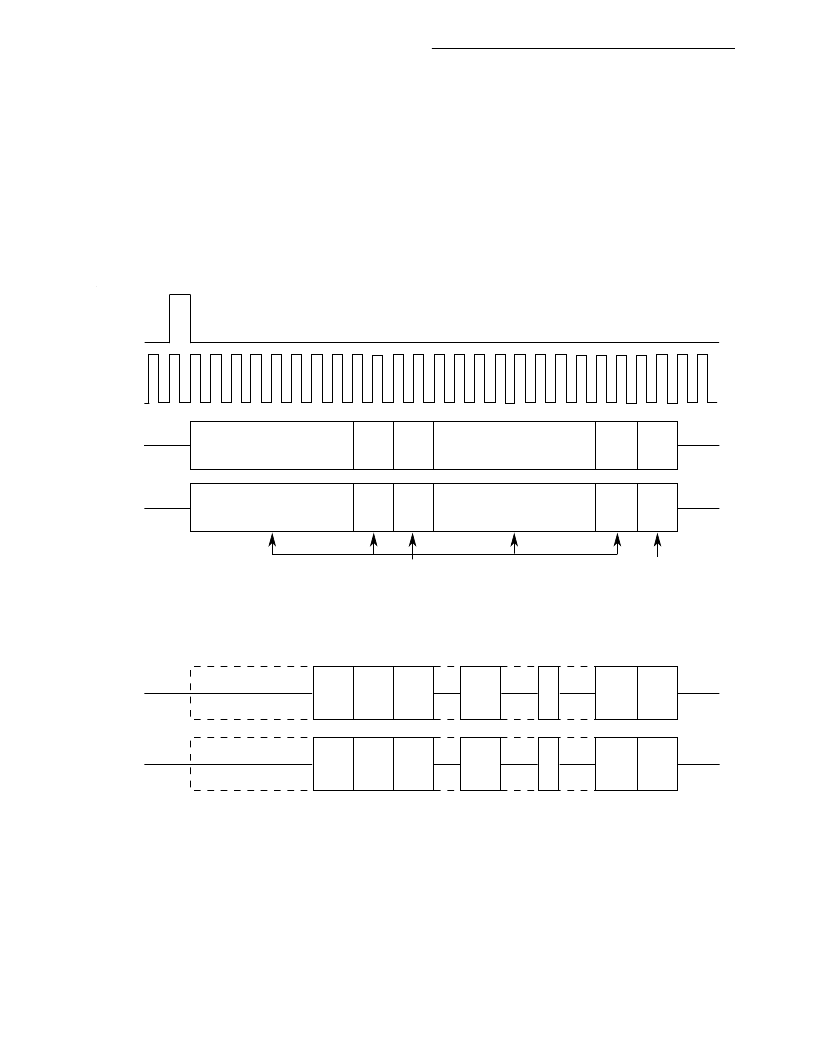

| 英文描述: | Integrated Multiprotocol Processor User’s Manual |

| 中文描述: | RISC PROCESSOR, PQFP132 |

| 封裝: | PLASTIC, QFP-132 |

| 文件頁數: | 131/480頁 |

| 文件大小: | 1815K |

| 代理商: | MC68302CFC20 |

相關PDF資料 |

PDF描述 |

|---|---|

| MC68302CRC16 | Integrated Multiprotocol Processor User’s Manual |

| MC68302CRC20 | Integrated Multiprotocol Processor User’s Manual |

| MC68302RC16 | Integrated Multiprotocol Processor User’s Manual |

| MC6802 | Microprocessor With Clock and Oprtional RAM |

| MC68B02P | Microprocessor With Clock and Oprtional RAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC68302CFC20C | 制造商:Motorola 功能描述:68302 |

| MC68302CFE16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Communications Controller |

| MC68302CFE20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Communications Controller |

| MC68302CPV16VC | 功能描述:IC MPU NETWORK 16MHZ 144-LQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:M683xx 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應商設備封裝:357-PBGA(25x25) 包裝:托盤 |

| *型號 | *數量 | 廠商 | 批號 | 封裝 |

|---|---|---|---|---|

|

|