- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383558 > MC-4R64FKE8D-653 (ELPIDA MEMORY INC) Direct Rambus DRAM RIMM Module 64M-BYTE (32M-WORD x 18-BIT) PDF資料下載

參數(shù)資料

| 型號(hào): | MC-4R64FKE8D-653 |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | Direct Rambus DRAM RIMM Module 64M-BYTE (32M-WORD x 18-BIT) |

| 中文描述: | 32M X 18 DIRECT RAMBUS DRAM MODULE, 53 ns, DMA184 |

| 封裝: | SOCKET TYPE, RIMM-184 |

| 文件頁(yè)數(shù): | 5/14頁(yè) |

| 文件大小: | 135K |

| 代理商: | MC-4R64FKE8D-653 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

Data Sheet E0080N20 (Ver 2.0)

5

MC-4R64FKE8D

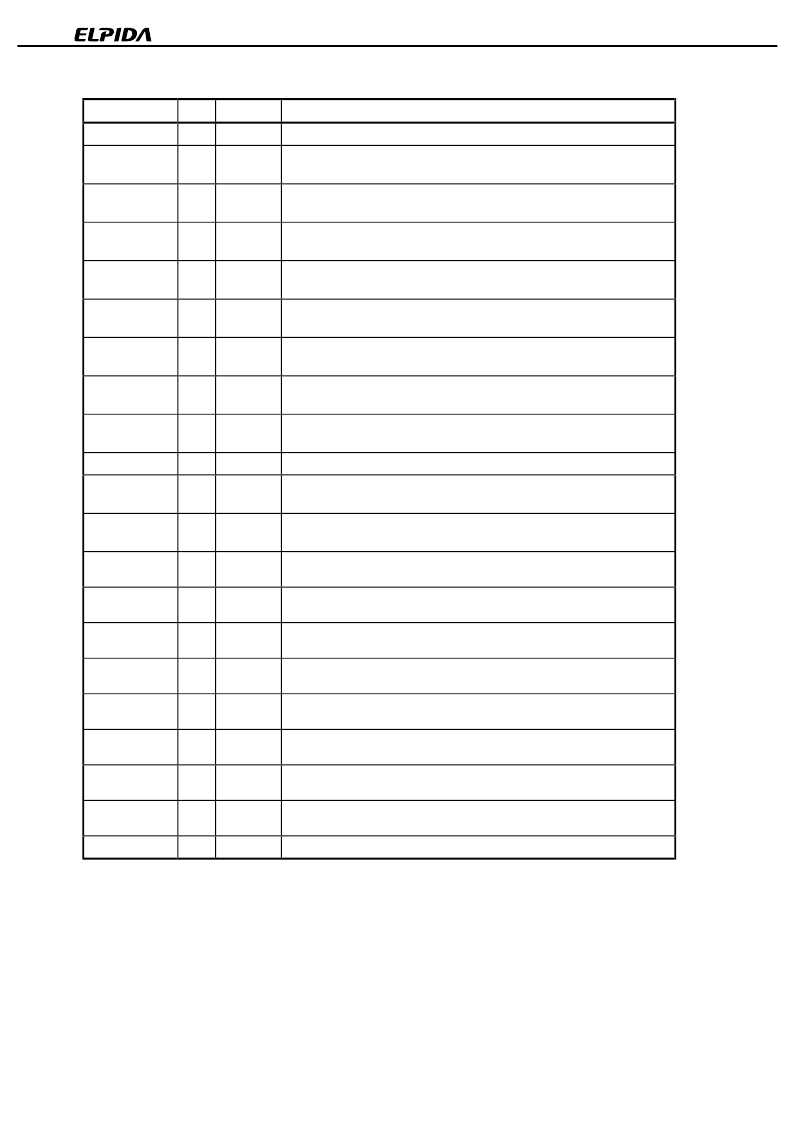

Module Connector Pad Description

(1/2)

Signal

I/O

Type

Description

GND

–

–

Ground reference for RDRAM core and interface. 72 PCB connector pads.

LCFM

I

RSL

Clock from master. Interface clock used for receiving RSL signals from the

Channel. Positive polarity.

LCFMN

I

RSL

Clock from master. Interface clock used for receiving RSL signals from the

Channel. Negative polarity.

LCMD

I

V

CMOS

Serial Command used to read from and write to the control registers. Also used

for power management.

LCOL4..LCOL0

I

RSL

Column bus. 5-bit bus containing control and address information for column

accesses.

LCTM

I

RSL

Clock to master. Interface clock used for transmitting RSL signals to the

Channel. Positive polarity.

LCTMN

I

RSL

Clock to master. Interface clock used for transmitting RSL signals to the

Channel. Negative polarity.

LDQA8..LDQA0

I/O

RSL

Data bus A. A 9-bit bus carrying a byte of read or write data between the Channel

and the RDRAM. LDQA8 is non-functional on modules with x16 RDRAM devices.

LDQB8..LDQB0

I/O

RSL

Data bus B. A 9-bit bus carrying a byte of read or write data between the Channel

and the RDRAM. LDQB8 is non-functional on modules with x16 RDRAM devices.

LROW2..LROW0

I

RSL

Row bus. 3-bit bus containing control and address information for row accesses.

LSCK

I

V

CMOS

Serial clock input. Clock source used to read from and write to the RDRAM

control registers.

NC

–

–

These pads are not connected. These 24 connector pads are reserved for future

use.

RCFM

I

RSL

Clock from master. Interface clock used for receiving RSL signals from the

Channel. Positive polarity.

RCFMN

I

RSL

Clock from master. Interface clock used for receiving RSL signals from the

Channel. Negative polarity.

RCMD

I

V

CMOS

Serial Command Input used to read from and write to the control registers. Also

used for power management.

RCOL4..RCOL0

I

RSL

Column bus. 5-bit bus containing control and address information for column

accesses.

RCTM

I

RSL

Clock to master. Interface clock used for transmitting RSL signals to the

Channel. Positive polarity.

RCTMN

I

RSL

Clock to master. Interface clock used for transmitting RSL signals to the

Channel. Negative polarity.

RDQA8..RDQA0

I/O

RSL

Data bus A. A 9-bit bus carrying a byte of read or write data between the Channel

and the RDRAM. RDQA8 is non-functional on modules with x16 RDRAM devices.

RDQB8..RDQB0

I/O

RSL

Data bus B. A 9-bit bus carrying a byte of read or write data between the Channel

and the RDRAM. RDQB8 is non-functional on modules with x16 RDRAM devices.

RROW2..RROW0

I

RSL

Row bus. 3-bit bus containing control and address information for row accesses.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC-4R64FKE8D-745 | QUICC |

| MC-4R96CEE6B | Direct Rambus DRAM RIMM Module 96M-BYTE 48M-WORD x 16-BIT |

| MC-4R96CEE6B-653 | Direct Rambus DRAM RIMM Module 96M-BYTE 48M-WORD x 16-BIT |

| MC-4R96CEE6B-745 | Direct Rambus DRAM RIMM Module 96M-BYTE 48M-WORD x 16-BIT |

| MC-4R96CEE6B-845 | Direct Rambus DRAM RIMM Module 96M-BYTE 48M-WORD x 16-BIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC-4R64FKE8D-745 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:Direct Rambus DRAM RIMM Module 64M-BYTE (32M-WORD x 18-BIT) |

| MC-4R64FKE8D-840 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:Direct Rambus DRAM RIMM Module 64M-BYTE (32M-WORD x 18-BIT) |

| MC-4R64FKE8D-845 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:Direct Rambus DRAM RIMM Module 64M-BYTE (32M-WORD x 18-BIT) |

| MC-4R64FKE8S | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:Direct Rambus DRAM SO-RIMM Module |

| MC-4R64FKE8S-840 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:Direct Rambus DRAM SO-RIMM Module |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。