- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382288 > MB89202P-SH (FUJITSU LTD) 8-Bit Proprietary Microcontroller PDF資料下載

參數(shù)資料

| 型號: | MB89202P-SH |

| 廠商: | FUJITSU LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-Bit Proprietary Microcontroller |

| 中文描述: | 8-BIT, MROM, 12.5 MHz, MICROCONTROLLER, PDIP32 |

| 封裝: | 1.778 MM PITCH, PLASTIC, DIP-32 |

| 文件頁數(shù): | 2/44頁 |

| 文件大小: | 427K |

| 代理商: | MB89202P-SH |

第1頁當前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

MB89202 Series

2

(Continued)

MB89F202 : Flash (at least 10,000 program / erase cycles) with read protection

Low-power consumption modes ( sleep mode, and stop mode)

SH-DIP-32, SSOP-34 package

CMOS Technology

■

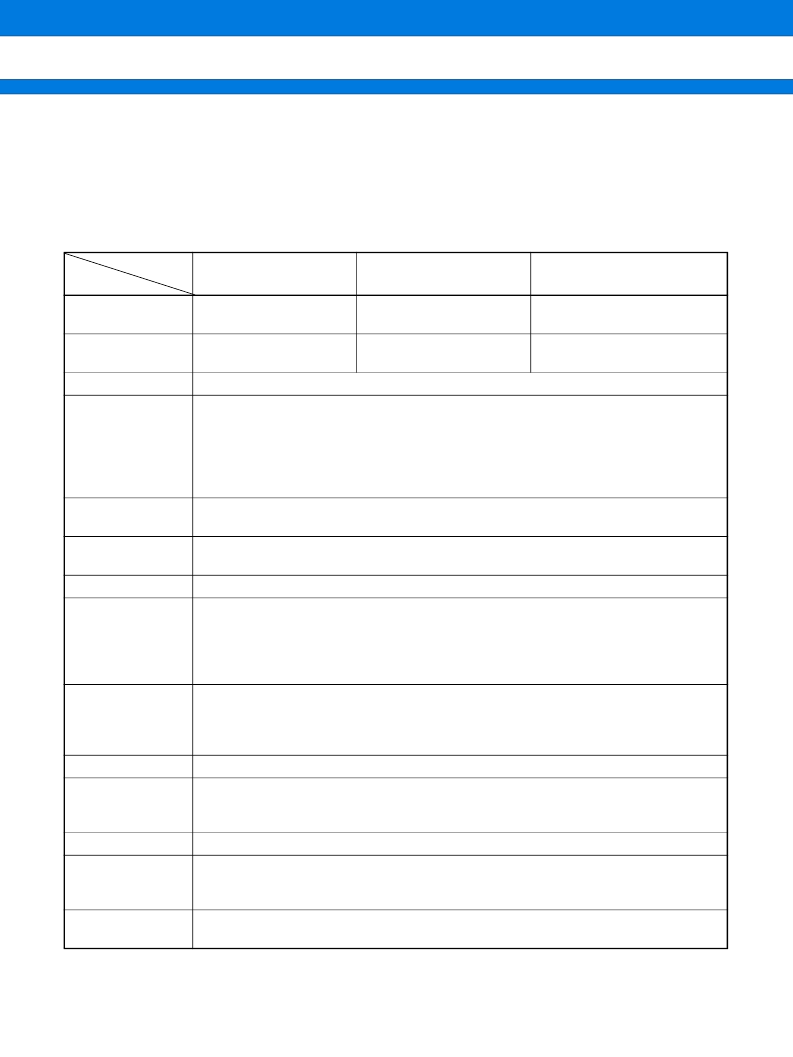

PRODUCT LINEUP

(Continued)

Part number

MB89202

MB89F202

MB89V201

Parameter

Classification

Mask ROM product

Flash memory product

(read protection)

16 K

×

8 bits

(internal flash)

512

×

8 bits

136

8 bits

1 to 3 bytes

1, 8, 16 bits

0.32

μ

s to 5.1

μ

s (12.5 MHz)

2.88

μ

s to 46.1

μ

s (12.5 MHz)

Evaluation product

(for development)

ROM size

16 K

×

8 bits

(internal mask ROM)

32K x 8 bits

(external EPROM)

RAM size

CPU functions

Number of instructions :

Instruction bit length :

Instruction length :

Data bit length :

Minimum execution time :

Interrupt processing time :

Ports

General-purpose I/O ports (CMOS) : 26 (also serve as peripherals )

(4 ports are also an N-ch open-drain type.)

21-bit time-base

timer

21-bit Interrupt cycle : 0.66 ms, 2.64 ms, 21 ms, or 335.5 ms with 12.5 MHz main clock

Watchdog timer

Reset generation cycle : 335.5 ms minimum with 12.5 MHz main clock

8-bit PWM timer

8-bit interval timer operation (square output capable, operating clock cycle :

0.32

μ

s , 2.56

μ

s, 5.1

μ

s, 20.5

μ

s)

8-bit resolution PWM operation (conversion cycle : 81.9

μ

s to 21.47 s : in the selection of

internal shift clock of 8/16-bit capture timer)

Count clock selectable between 8-bit and 16-bit timer/counter outputs

8-bit capture timer/counter

×

1 channel

+

8-bit timer or

16-bit capture timer/counter

×

1 channel

Capable of event count operation and square wave output using external clock input with

8-bit timer 0 or 16-bit counter

8/16-bit capture,

timer/counter

UART

Transfer data length : 6/7/8 bits

8-bit Serial I/O

8 bits LSB first/MSB first selectable

One clock selectable from four operation clocks

(one external shift clock, three internal shift clocks : 0.8

μ

s, 6.4

μ

s, 25.6

μ

s)

Output frequency : Pulse width and cycle selectable

12-bit PPG timer

External interrupt 1

(wake-up function)

3 channels (Interrupt vector, request flag, request output enabled)

Edge selectable (Rising edge, falling edge, or both edges)

Also available for resetting stop/sleep mode (Edge detectable even in stop mode)

External interrupt 2

(wake-up function)

1 channel with 8 inputs (Independent L-level interrupt and input enable)

Also available for resetting stop/sleep mode (Level detectable even in stop mode)

相關PDF資料 |

PDF描述 |

|---|---|

| MB89202PFV | 8-Bit Proprietary Microcontroller |

| MB89F202 | 8-Bit Proprietary Microcontroller |

| MB89F202P-SH | 8-Bit Proprietary Microcontroller |

| MB89F202PFV | 8-Bit Proprietary Microcontroller |

| MB89V201PFV | 8-Bit Proprietary Microcontroller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MB89251A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:SERIAL DATA TRANSMITTER / RECEIVER |

| MB89254 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:PROGRAMMABLE TIMER |

| MB89255A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:PARALLEL DATA I/O INTERFACE |

| MB89259A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:INTERRUPT CONTROLLER |

| MB89322B | 制造商:Fuji Electric 功能描述:89322B 制造商:FUJITSU 功能描述:89322B |

發(fā)布緊急采購,3分鐘左右您將得到回復。