- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16779 > MAX9888EVKIT+ (Maxim Integrated Products)KIT EVALUATION FOR MAX9888 PDF資料下載

參數(shù)資料

| 型號: | MAX9888EVKIT+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 9/115頁 |

| 文件大小: | 0K |

| 描述: | KIT EVALUATION FOR MAX9888 |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 1 |

| 系列: | DirectDrive®, FLEXSOUND™ |

| 相關(guān)產(chǎn)品: | MAX9888EWY+T-ND - IC CODEC AUDIO FLEXSOUND 63WLP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁

Stereo Audio CODEC

with FlexSound Technology

MAX9888

106

The slave address with the R/W bit set to 0 indicates

that the master intends to write data to the IC. The IC

acknowledges receipt of the address byte during the

master-generated 9th SCL pulse.

The second byte transmitted from the master configures

the IC’s internal register address pointer. The pointer

tells the IC where to write the next byte of data. An

acknowledge pulse is sent by the IC upon receipt of the

address pointer data.

The third byte sent to the IC contains the data that is

written to the chosen register. An acknowledge pulse

from the IC signals receipt of the data byte. The address

pointer autoincrements to the next register address after

each received data byte. This autoincrement feature

allows a master to write to sequential registers within

one continuous frame. The master signals the end of

transmission by issuing a STOP condition. Register

addresses greater than 0xC7 are reserved. Do not write

to these addresses.

Read Data Format

Send the slave address with the R/W bit set to 1 to initi-

ate a read operation. The IC acknowledges receipt of

its slave address by pulling SDA low during the 9th SCL

clock pulse. A START command followed by a read com-

mand resets the address pointer to register 0x00.

The first byte transmitted from the IC is the content of

register 0x00. Transmitted data is valid on the rising

edge of SCL. The address pointer autoincrements after

each read data byte. This autoincrement feature allows

all registers to be read sequentially within one continu-

ous frame. A STOP condition can be issued after any

number of read data bytes. If a STOP condition is issued

followed by another read operation, the first data byte to

be read is from register 0x00.

The address pointer can be preset to a specific register

before a read command is issued. The master presets

the address pointer by first sending the IC’s slave

address with the R/W bit set to 0 followed by the register

address. A REPEATED START condition is then sent fol-

lowed by the slave address with the R/W bit set to 1. The

IC then transmits the contents of the specified register.

The address pointer autoincrements after transmitting

the first byte.

The master acknowledges receipt of each read byte

during the acknowledge clock pulse. The master must

acknowledge all correctly received bytes except the last

byte. The final byte must be followed by a not acknowl-

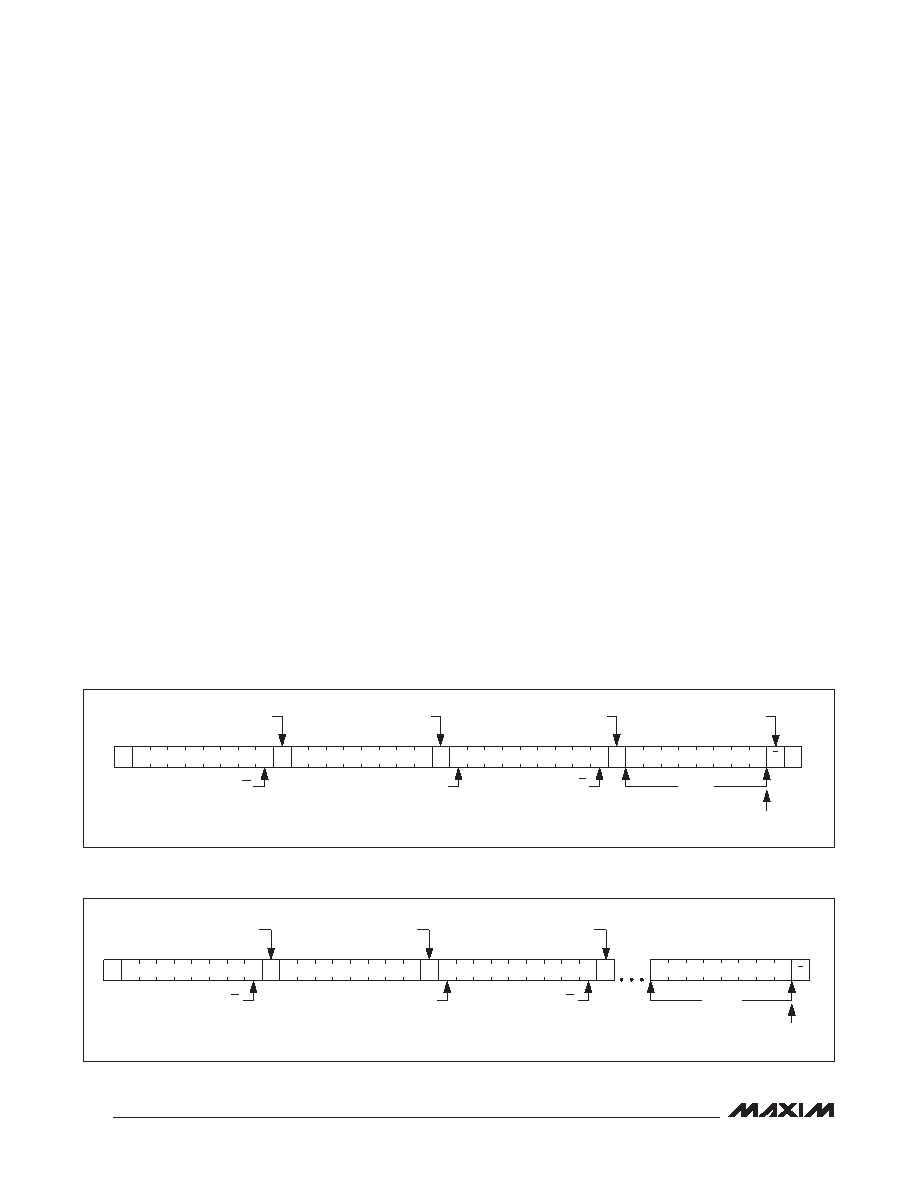

edge from the master and then a STOP condition. Figure

37 illustrates the frame format for reading one byte from

the IC. Figure 38 illustrates the frame format for reading

multiple bytes from the IC.

Figure 37. Reading One Byte of Data from the IC

Figure 38. Reading n Bytes of Data from the IC

ACKNOWLEDGE FROM MAX9888

NOT ACKNOWLEDGE FROM MASTER

AUTOINCREMENT INTERNAL REGISTER ADDRESS POINTER

1 BYTE

P

REPEATED START

S

O A

A Sr

1

A

SLAVE ADDRESS

REGISTER ADDRESS

SLAVE ADDRESS

DATA BYTE

R/W

ACKNOWLEDGE FROM MAX9888

AUTOINCREMENT INTERNAL REGISTER ADDRESS POINTER

1 BYTE

REPEATED START

S

O

A

Sr

1

A

SLAVE ADDRESS

REGISTER ADDRESS

SLAVE ADDRESS

DATA BYTE

R/W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| H3AAH-3418G | IDC CABLE - HSC34H/AE34G/HSC34H |

| EBM22DRAI | CONN EDGECARD 44POS R/A .156 SLD |

| RNF-100-1/8-GN-STK | HEAT SHRINK TUBING |

| RSC06DREF-S13 | CONN EDGECARD 12POS .100 EXTEND |

| GEC26DRXN-S734 | CONN EDGECARD 52POS DIP .100 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9888EVKIT+ | 功能描述:音頻 IC 開發(fā)工具 MAX9888 Eval Kit RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| MAX9888EWY+T | 功能描述:接口—CODEC Stereo Audio CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| MAX9889EWO+T | 功能描述:接口—CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| MAX988ESA | 功能描述:校驗器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 產(chǎn)品: 比較器類型: 通道數(shù)量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應(yīng)時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

| MAX988ESA+ | 功能描述:校驗器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 產(chǎn)品: 比較器類型: 通道數(shù)量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應(yīng)時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。