- 您現在的位置:買賣IC網 > PDF目錄296470 > MAX9851EVCMODU (MAXIM INTEGRATED PRODUCTS INC) MAX9851評估板/評估系統(tǒng) PDF資料下載

參數資料

| 型號: | MAX9851EVCMODU |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 編解碼器 |

| 英文描述: | MAX9851評估板/評估系統(tǒng) |

| 中文描述: | PCM CODEC |

| 文件頁數: | 43/73頁 |

| 文件大?。?/td> | 1357K |

| 代理商: | MAX9851EVCMODU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

MAX9851/MAX9853

Stereo Audio CODECs with Microphone, DirectDrive

Headphones, Speaker Amplifiers, or Line Outputs

48

______________________________________________________________________________________

Master Mode (S1MAS/S2MAS)

1 = Master mode (LRCLK and BCLK timing signals

generated internally; LRCLK and BCLK configured as

outputs).

0 = Slave mode (LRCLK and BCLK accepted from

external source; LRCLK and BCLK configured as

inputs).

Slave mode timing signals may operate asynchronous

to either the MCLK or the other audio interface source

in DAC-only stereo audio modes. An interface with the

ADC output enabled must operate in master mode,

unless operating synchronously in voice mode.

LRCLK Invert (S1WCI/S2WCI)

1 = Right-channel data is transmitted while LRCLK is

low.

0 = Left-channel data is transmitted while LRCLK is

low.

Set S1WCI/S2WCI = 0 to conform to the I2S standard.

S1WCI/S2WCI have no effect in voice mode.

BCLK Invert (S1BCI/S2BCI)

1 = Digital audio bits are transferred on the falling edge

of BCLK.

0 = Digital audio bits are transferred on the rising edge

of BCLK.

Set S1BCI/S2BCI = 0 to conform to the I2S standard.

Data Delay (S1DLY/S2DLY)

1 = Digital audio MSB on SDIN and SDOUT is trans-

ferred on the 2nd BCLK edge following an LRCLK edge.

0 = Digital audio MSB on SDIN and SDOUT is trans-

ferred on the 1st BCLK edge following an LRCLK edge.

Set S1DLY/S2DLY = 1 to conform to the I2S standard.

S1DLY/S2DLY have no effect in voice mode.

Word Size (S1WS/S2WS)

1 = 18-bit digital audio data.

0 = 16-bit digital audio data.

When operating in master mode, the number of BLCK

cycles per sample corresponds to the word size select-

ed by S1WS/S2WS. S1WS/S2WS have no effect in

voice mode.

MCLK Frequency Mode (MHz)

1 = 26MHz MCLK.

0 = 13MHz MCLK.

A 26MHz clock allows for synchronous 16kHz voice

mode. All other modes of operation can operate from

either MCLK frequency.

ADC DC-Blocking Filter Enable (ADCDC)

1 = ADC DC block enabled.

0 = ADC DC block disabled.

DC-blocking consists of a highpass filter with a cutoff

frequency of fS / 1608. This filter is available in all modes

of operation including voice modes. The ADC DC-

blocking filter can be overloaded with low-frequency

signals with DC offset greater than ±0.125V (one-eighth

full scale).

ADC Bandpass Filter Enable (ABPE)

1 = ADC bandpass filter enabled.

0 = ADC bandpass filter disabled.

ABPE = 1 enables the ADC highpass filter in combina-

tion with the ADC lowpass filter to create a bandpass

filter. The ADC voiceband filters only operate on the left

output channel data of voiceband, the ADC, and when

operating in voice mode.

DAC Bandpass Filter Enable (DBPE)

1 = DAC bandpass filter enabled.

0 = DAC bandpass filter disabled.

DBPE = 1 enables the DAC highpass filter in combina-

tion with the DAC lowpass filter to create a bandpass

filter. The DAC filters only operate on the S1 left input or

mono S1 L+R input signal data.

Left and Right DAC Highpass Filter Mode

(DHPL/DHPR)

00 = No filtering.

01 = 55Hz to 91Hz cutoff frequency.

10 = 171Hz to 279Hz cutoff frequency.

11 = 327Hz to 533Hz cutoff frequency.

When both the ADC and DAC are enabled, the exact

cutoff frequency of each setting depends on the sam-

ple rate in use. In DAC-only mode, the exact cutoff fre-

quency will be the high end of the range above.

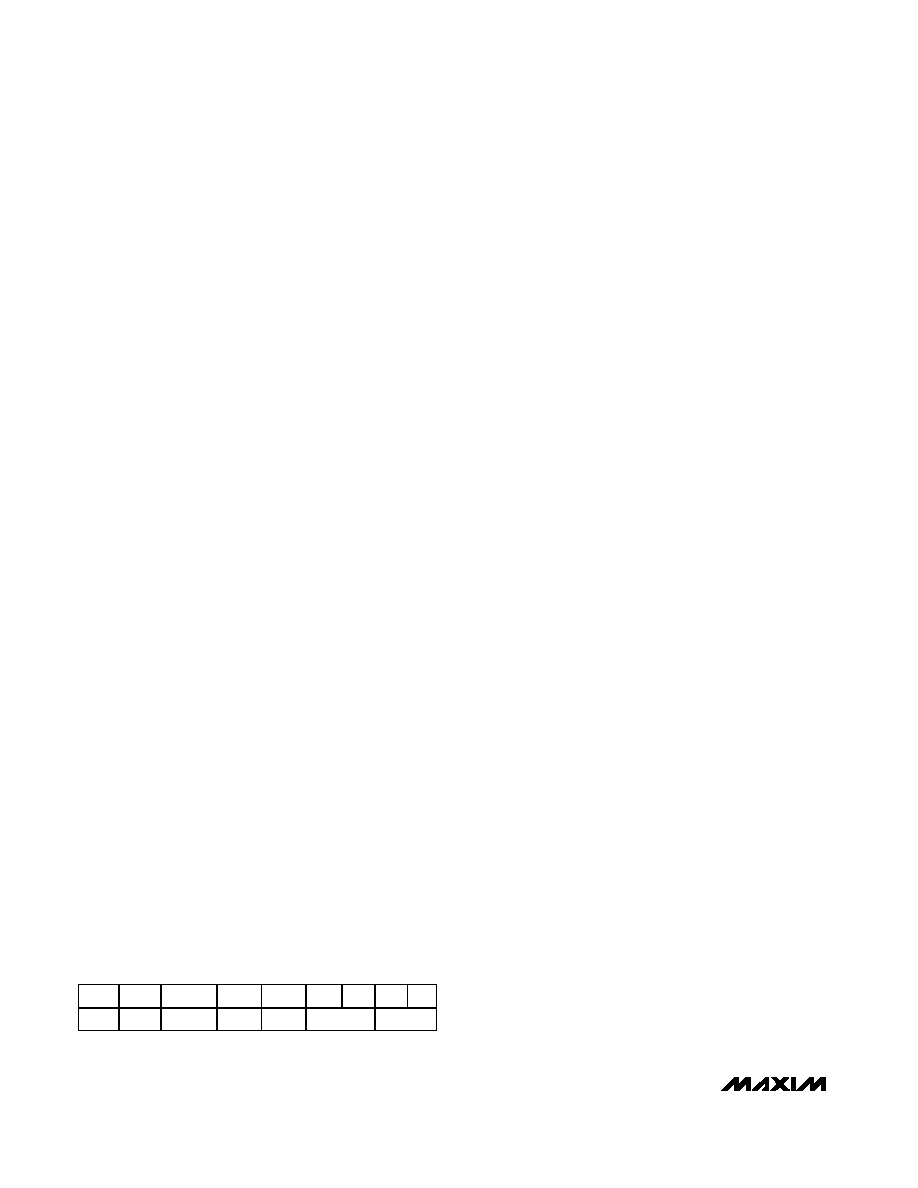

Table 14. Digital Filter

REG

B7

B6

B5

B4

B3

B2

B1

B0

0x07

MHZ

ADCDC

ABPE

DBPE

DHPL

DHPR

Digital Filter Register (0x07)

相關PDF資料 |

PDF描述 |

|---|---|

| MAX9934FART+T | SPECIALTY ANALOG CIRCUIT, PBGA6 |

| MAX9950FCCB | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| MAX9966BGCCQ+D | Quad, Low-Power, 500Mbps ATE Driver/Comparator |

| MAXQ2000-QBX | Low-Power LCD Microcontroller |

| MAYK062DG | 6.2 V, 0.2 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MAX9851EVKIT | 功能描述:音頻 IC 開發(fā)工具 Evaluation Kit/Evaluation System for the MAX9851 RoHS:否 制造商:Texas Instruments 產品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| MAX9853ETM+ | 功能描述:接口—CODEC Stereo Audio CODEC w/DirectDrive Amp RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| MAX9853ETM+T | 功能描述:接口—CODEC Stereo Audio CODEC w/DirectDrive Amp RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| MAX9853EVCMODU | 功能描述:音頻 IC 開發(fā)工具 Evaluation Kit/Evaluation System for the MAX9853 RoHS:否 制造商:Texas Instruments 產品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| MAX9853EVKIT | 功能描述:音頻 IC 開發(fā)工具 Evaluation Kit/Evaluation System for the MAX9853 RoHS:否 制造商:Texas Instruments 產品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。