- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1936 > MAX14821ETG+ (Maxim Integrated Products)IC IO-LINK 24-TQFN PDF資料下載

參數(shù)資料

| 型號(hào): | MAX14821ETG+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 18/31頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC IO-LINK 24-TQFN |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 25 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)

MAX14821

IO-Link Device Transceiver

25

Maxim Integrated

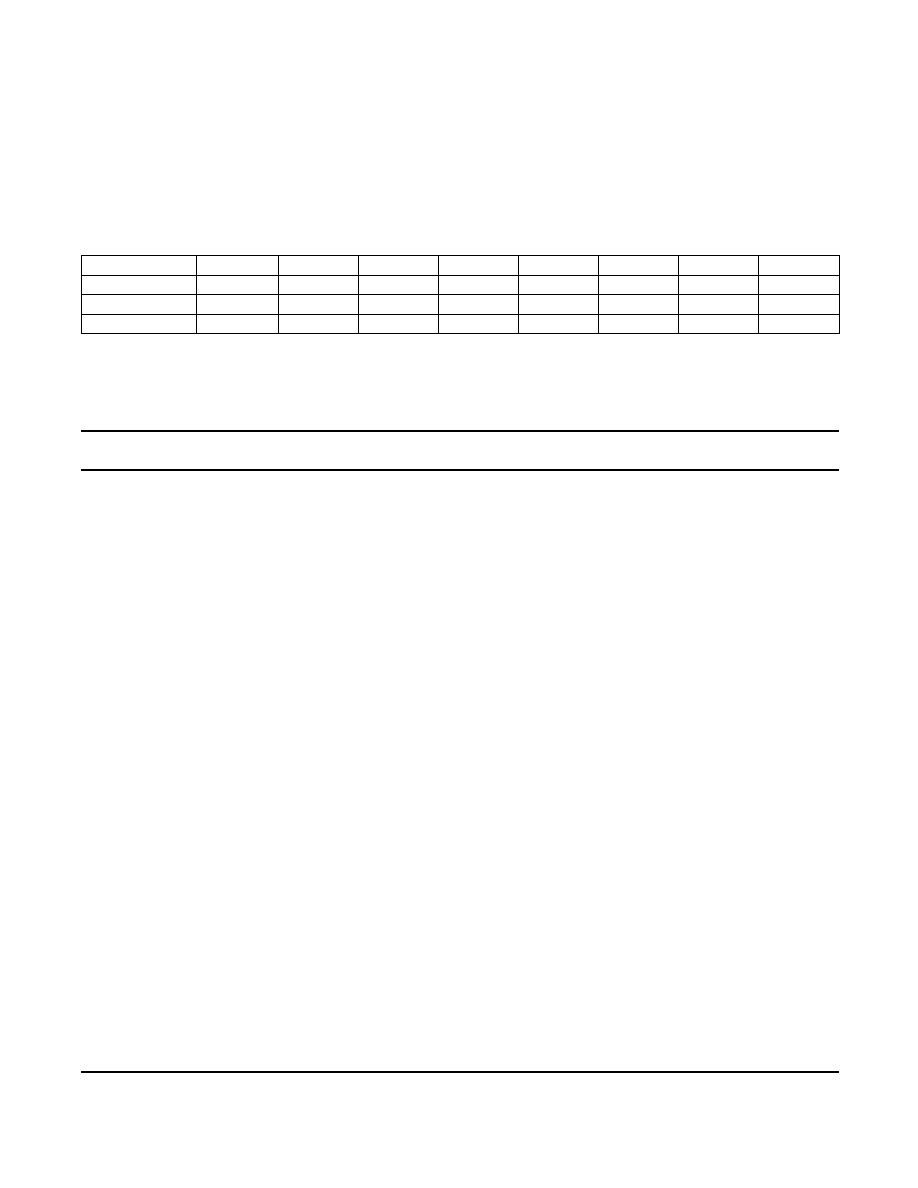

Mode Register [R1, R0] = [1,1]

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Bit Name

RST

WuIntEn

DoFault

C/QFault

UV24

OTemp

UV33En

LDO33Dis

Read/Write

R/W

R

R/W

POR State

0

Use the Mode register to reset the MAX14821 and manage the 3.3V LDO. The Mode register has bits that repre-

sent the current status of fault conditions. When writing to the Mode register, the contents of the fault indication bits

(bits 2 to 5) do not change.

BIT

NAME

DESCRIPTION

D7

RST

Register Reset. Set RST to 1 to reset all registers to their default power-up state. Then

set RST to 0 for normal operation.

The Status register is cleared and IRQ deasserts (if asserted) when RST = 1. Interrupts

are not generated while RST = 1.

D6

WuIntEn

Wake-Up Interrupt Enable. Set WuIntEn to 1 to enable wake-up interrupt generation.

When WuIntEn is set, the WuInt bit in the Status register is set and IRQ asserts when

a valid wake-up condition is detected. The C/Q driver must be enabled for wake-up

detection. The state of WuIntEn does not affect the WU output. See the Wake-Up

Detection section for more information.

D5

DoFault

DO Fault Status. The DoFault bit is set when a short circuit or voltage fault occurs at

the DO driver output (see the DO Fault Detection section for more information). The

DoFault and DoFaultInt bits are both set when a fault occurs on DO. DoFault is cleared

when the fault is removed.

D4

C/QFault

C/Q Fault Status. The C/QFault bit is set when a short circuit or voltage fault occurs at

the C/Q driver output (see the C/Q Fault Detection section for more information). The

C/QFault and C/QFaultInt bits are both set when a fault occurs on C/Q. C/QFault is

cleared when the fault is removed.

D3

UV24

VCC Undervoltage Condition. Both the UV24 and the UV24Int bits are set when VCC

falls below VCCUVLO. UV24 is cleared when VCC rises above the VCC threshold. V5

must be present for VCC undervoltage monitoring.

D2

OTemp

Temperature Warning. The OTemp bit is set when a high-temperature condition

occurs on the device. Both the OTempInt interrupt in the Status register and the OTemp

bit are set when the junction temperature of the die rises to above +115NC (typ). The

OTemp bit is cleared when the junction temperature falls below +95NC (typ).

D1

UV33En

LDO33 UV Enable. Set the UV33En bit to 1 to assert the UV output when LDO33 volt-

age falls below the 2.4V (typ) undervoltage-lockout threshold. The UV33En bit does

not affect the UV33Int bit in the Status register; IRQ asserts when VLDO33 falls below

VLDO33UVLO regardless of the state of UV33En.

D0

LDO33Dis

LDO33 Enable/Disable. Set LDO33Dis to 1 to disable the 3.3V linear regulator (LDO33).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX14824GTG+ | IC IO-LINK MASTER TXRX 24TQFN |

| MAX1482CSD-T | IC TXRX RS485/422 250KBPS 14SOIC |

| MAX14830ETM+ | SEMICONDUCTOR OTHER |

| MAX14841EASA+T | IC TXRX RS485 40MBPS 8SOIC |

| MAX1484CUB+ | IC TXRX RS485/RS422 10-UMAX |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX14821ETG+ | 功能描述:輸入/輸出控制器接口集成電路 NEW RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| MAX14821ETG+T | 功能描述:輸入/輸出控制器接口集成電路 NEW RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| MAX14821EVKIT# | 功能描述:界面開發(fā)工具 MAX14820/21 EVAL KIT RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| MAX14821EWA+ | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

| MAX14821EWA+T | 功能描述:輸入/輸出控制器接口集成電路 100mA IO-Link Transceiver RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。