- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384638 > M470L3223DT0-CLB3 (SAMSUNG SEMICONDUCTOR CO. LTD.) 256MB DDR SDRAM MODULE PDF資料下載

參數(shù)資料

| 型號: | M470L3223DT0-CLB3 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256MB DDR SDRAM MODULE |

| 中文描述: | 256MB的DDR內(nèi)存模塊 |

| 文件頁數(shù): | 12/16頁 |

| 文件大?。?/td> | 171K |

| 代理商: | M470L3223DT0-CLB3 |

M470L3223DT0

Rev. 0.0 Dec. 2001

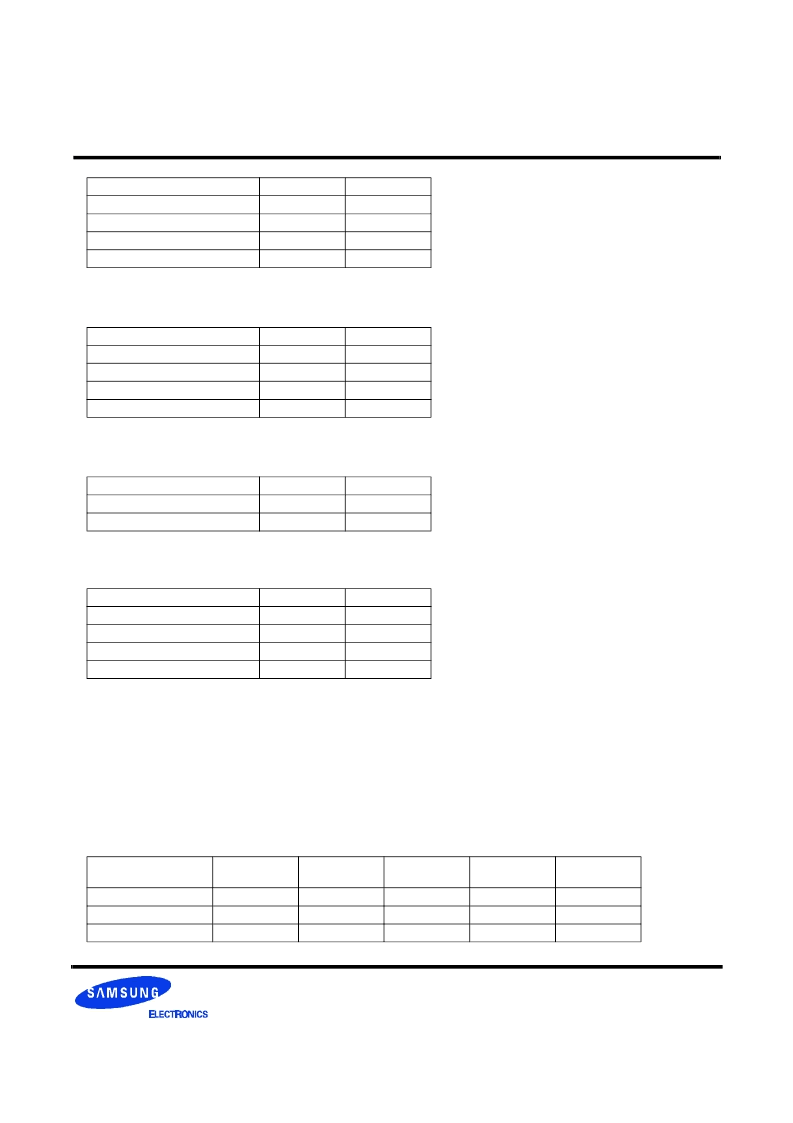

6. Input Setup/Hold Slew Rate Derating

This derating table is used to increase t

IS

/t

IH

in the case where the input slew rate is below 0.5V/ns. Input setup/hold slew rate

based on the lesser of AC-AC slew rate and DC-DC slew rate.

7. I/O Setup/Hold Slew Rate Derating

This derating table is used to increase t

DS

/t

DH

in the case where the I/O slew rate is below 0.5V/ns. I/O setup/hold slew rate

based on the lesser of AC-AC slew rate and DC-DC slew rate.

8. I/O Setup/Hold Plateau Derating

This derating table is used to increase tDS/tDH in the case where the input level is flat below VREF

±

310mV for a duration of

up to 2ns.

9. I/O Delta Rise/Fall Rate(1/slew-rate) Derating

This derating table is used to increase t

DS

/t

DH

in the case where the DQ and DQS slew rates differ. The Delta Rise/Fall Rate

is calated as 1/SlewRate1-1/SlewRate2. For example, if slew rate 1 = 5V/ns and slew rate 2 =.4V/ns then the Delta Rise/Fall

Rate =-0/5ns/V. Input S/H slew rate based on larger of AC-AC delta rise/fall rate and DC-DC delta rise/fall rate.

10. This parameter is fir system simulation purpose. It is guranteed by design.

11. For each of the terms, if not already an integer, round to the next highest integer. tCK is actual to the system clock cycle time.

Input Setup/Hold Slew Rate

tIS

(ps)

tIH

(ps)

(V/ns)

0.5

0

0

0.4

+50

+50

0.3

+100

+100

I/O Setup/Hold Slew Rate

tDS

(ps)

tDH

(ps)

(V/ns)

0.5

0

0

0.4

+75

+75

0.3

+150

+150

I/O Input Level

tDS

(ps)

tDH

(ps)

(mV)

±

280

+50

+50

Delta Rise/Fall Rate

tDS

(ps)

tDH

(ps)

(ns/V)

0

0

0

±

0.25

±

0.5

+50

+50

+100

+100

The following table specifies derating values for the specifications listed if the single-ended clock skew rate is less than 1.0V/ns.

tIH/tIS

(ps)

(ps)

CK slew rate

(Single ended)

tDSS/tDSH

tAC/tDQSCK

(ps)

tLZ(min)

(ps)

tHZ(max)

(ps)

1.0V/ns

0

0

0

0

0

0.75V/ns

+50

+50

+50

-50

+50

0.5V/ns

+100

+100

+100

-100

+100

<Note>

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M470L3223DT0 | 256MB DDR SDRAM MODULE |

| M470L3223DT0-CA0 | 256MB DDR SDRAM MODULE |

| M470L3223DT0-CA2 | 256MB DDR SDRAM MODULE |

| M470L3223DT0-CB0 | 256MB DDR SDRAM MODULE |

| M470L3223DT0-CB3 | 256MB DDR SDRAM MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M470L3224BT0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224BTO | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224DT0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224DT0-CA0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224DT0-CA2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。