- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45001 > LTM9005CV-AA#PBF (LINEAR TECHNOLOGY CORP) SPECIALTY ANALOG CIRCUIT, PBGA204 PDF資料下載

參數(shù)資料

| 型號: | LTM9005CV-AA#PBF |

| 廠商: | LINEAR TECHNOLOGY CORP |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PBGA204 |

| 封裝: | 22 X 15 MM, 4.32 MM HEIGHT, LEAD FREE, MO-222, LGA-204 |

| 文件頁數(shù): | 8/24頁 |

| 文件大小: | 468K |

| 代理商: | LTM9005CV-AA#PBF |

LTM9005

16

9005p

applicaTions inForMaTion

Custommatchingnetworkscanbedesignedusingtheport

impedance data listed in Table 2. This data is referenced

to the LO pin with no external matching.

Table 2 LO Input Impedance vs Frequency

FREQUENCY

(MHz)

INPUT

IMPEDANCE

S11

MAG

ANGLE

50

10.0 – j326

0.991

–17.4

300

80.5 – j41.9

0.820

–99.2

500

11.8 – j10.1

0.632

–155.9

700

18.8 + j10.9

0.474

151.8

900

35.0 + j27.4

0.350

100.8

1200

72.9 + j19.3

0.241

31.3

1500

70.0 – j12.6

0.196

–26.1

1800

55.0 – j17.0

0.167

–64.3

2200

47.8 – j9.7

0.102

–97.2

2600

53.6 – j1.9

0.039

–26.8

3000

66.7 + j0.7

0.143

2.1

3500

82.1 – j13.9

0.263

–17.4

4000

69.0 – j30.1

0.290

–43.5

4500

43.7 – j13.2

0.154

–107.5

5000

36.4 + j19.8

0.271

111.6

LO Input Overload

Text to come.

Reference Operation

The LTM9005 includes an internal voltage reference that

is internally bypassed. An external reference can be used

or the internal reference can be configured for two pin

selectableinputranges.TyingtheSENSEpintoVDDselects

the default range; tying the SENSE pin to 1.5V selects a

3dB lower range.

Other voltage ranges in-between the pin selectable ranges

can be programmed. An external reference can be used by

applying its output directly or through a resistive divider

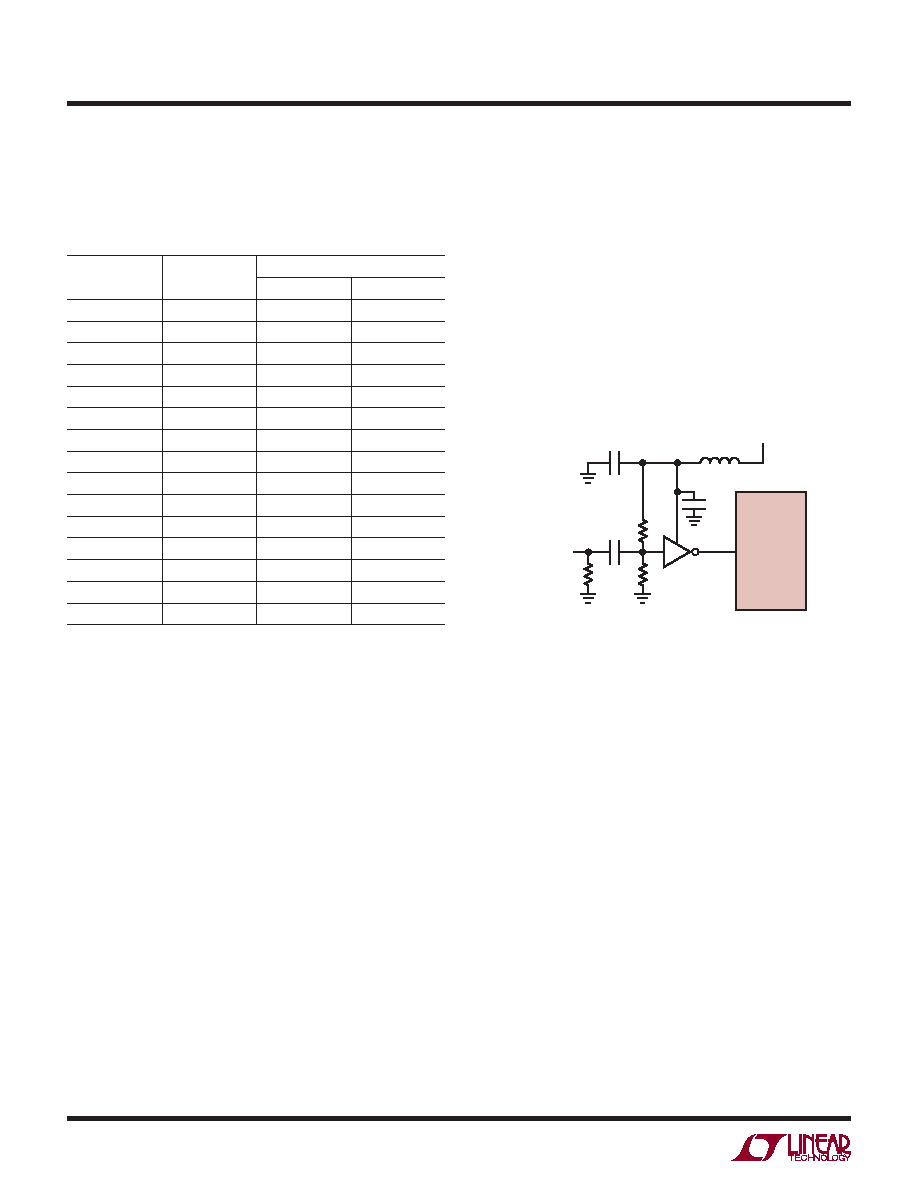

Figure 8. Sinusoidal Single-Ended CLK Driver

to SENSE. It is not recommended to drive the SENSE pin

with a logic device. The SENSE pin should be tied to the

appropriate level as close to the converter as possible. If

the SENSE pin is driven externally, note that this pin is

filtered internally with a 50Ω series resistor and a 0.1F

capacitor to ground.

ADC Clock Input

The CLK input can be driven directly with a CMOS or TTL

levelsignal.Asinusoidalclockcanalsobeusedalongwitha

low-jitter squaring circuit before the CLK pin (Figure 8).

CLK

50

0.1F

4.7F

1k

FERRITE

BEAD

CLEAN

SUPPLY

SINUSOIDAL

CLOCK

INPUT

9005 F08

NC7SVU04

LTM9005

The noise performance of the ADC can depend on the

clock signal quality as much as on the analog input. Any

noise present on the CLK signal will result in additional

aperture jitter that will be RMS summed with the inherent

ADC aperture jitter.

In applications where jitter is critical, use as large an

amplitude as possible. Also, if the ADC is clocked with a

sinusoidal signal, filter the CLK signal to reduce wideband

noise and distortion products generated by the source.

Figure 9 and Figure 10 show alternatives for converting a

differential clock to the single-ended CLK input. The use

of a transformer provides no incremental contribution

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTM9005CV-AB#PBF | SPECIALTY ANALOG CIRCUIT, PBGA204 |

| LTM9005IV-AB#PBF | SPECIALTY ANALOG CIRCUIT, PBGA204 |

| LUCW3000ACN-TR | PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO14 |

| LUCW3000ACN | PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO14 |

| LUCW3000ACN | PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LTM9005GD | 功能描述:LED 電路板指示器 Vert LED Assmbly 5mm Green RoHS:否 制造商:Lumex LED 大小:3 mm 照明顏色:Green 波長:565 nm 光強(qiáng)度:30 mcd 安裝類型:SMD/SMT 顯示角:60 deg 封裝:Reel |

| LTM9006-14 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:14-Bit, 65Msps/40Msps/25Msps Low Power Octal ADCs |

| LTM9006CY-14#PBF | 制造商:Linear Technology 功能描述:IC ADC 14BIT SPI/SRL 25M 140-BGA 制造商:Linear Technology 功能描述:ADC 8CH 1.8V 14BIT 25MSPS 制造商:Linear Technology 功能描述:ADC, 14BIT, 25MSPS, SPI, BGA-140; Resolution (Bits):14bit; Sampling Rate:25MSPS; Supply Voltage Type:Single; Supply Voltage Min:1.7V; Supply Voltage Max:1.9V; Supply Current:175mA; Digital IC Case Style:BGA; No. of Pins:140 ;RoHS Compliant: Yes |

| LTM9006IY-14#PBF | 制造商:Linear Technology 功能描述:IC ADC 14BIT SPI/SRL 25M 140-BGA 制造商:Linear Technology 功能描述:MS-uModule, 14-bit, 25Msps, 1.8V Octal ADC, Serial LVDS Outputs |

| LTM9007-14 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:14-Bit, 65Msps/40Msps/25Msps Low Power Octal ADCs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。