- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385492 > LMX2486 (National Semiconductor Corporation) 1.0 GHz - 4.5 GHz High Performance Delta-Sigma Low Power Dual PLLatinum TM Frequency Synthesizers with 3.0 GHz Integer PLL PDF資料下載

參數(shù)資料

| 型號: | LMX2486 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | 1.0 GHz - 4.5 GHz High Performance Delta-Sigma Low Power Dual PLLatinum TM Frequency Synthesizers with 3.0 GHz Integer PLL |

| 中文描述: | 1.0千兆赫- 4.5吉赫高性能Δ-Σ低功耗雙PLLatinum商標頻率合成器與整數(shù)的3.0 GHz鎖相環(huán) |

| 文件頁數(shù): | 34/37頁 |

| 文件大小: | 870K |

| 代理商: | LMX2486 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁

Programming Description

(Continued)

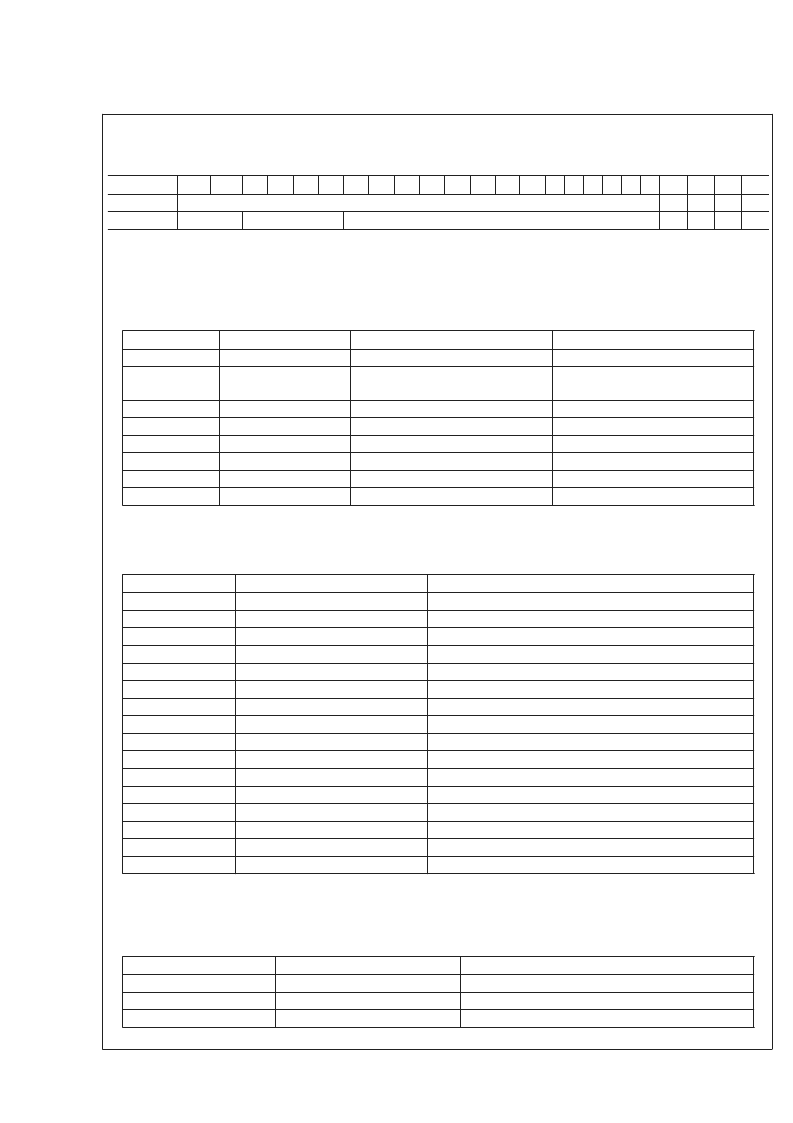

2.7 R6 REGISTER

REGISTER

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DATA[19:0]

C3

1

C2

1

C1

0

C0

1

R6

CSR[1:0]

RF_CPF[3:0]

RF_TOC[13:0]

2.7.1 RF_TOC -- RF Time Out Counter and Control for FLoutRF Pin

The RF_TOC[13:0] word controls the operation of the RF Fastlock circuitry as well as the function of the FLoutRF output pin.

When this word is set to a value between 0 and 3, the RF Fastlock circuitry is disabled and the FLoutRF pin operates as a general

purpose CMOS TRI-STATE I/O. When RF_TOC is set to a value between 4 and 16383, the RF Fastlock mode is enabled and

the FLoutRF pin is utilized as the RF Fastlock output pin. The value programmed into the RF_TOC[13:0] word represents two

times the number of phase detector comparison cycles the RF synthesizer will spend in the Fastlock state.

RF_TOC

0

1

Fastlock Mode

Disabled

Manual

Fastlock Period [CP events]

N/A

N/A

FLoutRF Pin Functionality

High Impedance

Logic “0” State.

Forces all Fastlock conditions

Logic “0” State

Logic “1” State

Fastlock

Fastlock

Fastlock

Fastlock

2

3

4

5

…

Disabled

Disabled

Enabled

Enabled

Enabled

Enabled

N/A

N/A

4X2 = 8

5X2 = 10

…

16383X2 = 32766

16383

2.7.2 RF_CPF -- RF PLL Fastlock Charge Pump Current

Specify the charge pump current for the Fastlock operation mode for the RF PLL. Note that the Fastlock charge pump current,

steady state current, and CSR control are all interrelated.

RF_CPF

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

RF Charge Pump State

1X

2X

3X

4X

5X

6X

7X

8X

9X

10X

11X

12X

13X

14X

15X

16X

Typical RF Charge Pump Current at 3 Volts (μA)

95

190

285

380

475

570

665

760

855

950

1045

1140

1235

1330

1425

1520

2.7.3 CSR[1:0] -- RF Cycle Slip Reduction

CSR controls the operation of the Cycle Slip Reduction Circuit. This circuit can be used to reduce the occurrence of phase

detector cycle slips. Note that the Fastlock charge pump current, steady state current, and CSR control are all interrelated. Refer

to section 1.8 for information on how to use this.

CSR

0

1

2

CSR State

Disabled

Enabled

Enabled

Sample Rate Reduction Factor

1

1/2

1/4

L

www.national.com

34

相關PDF資料 |

PDF描述 |

|---|---|

| LMX2487E | 7.5 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 3.0 GHz Integer PLL |

| LMX2487ESQ | 7.5 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 3.0 GHz Integer PLL |

| LMX2487ESQX | 7.5 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 3.0 GHz Integer PLL |

| LMX2515 | PLLatinum⑩ Frequency Synthesizer System with Integrated VCO |

| LMX2515LQ0701 | PLLatinum⑩ Frequency Synthesizer System with Integrated VCO |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LMX2486EVAL | 功能描述:時鐘和定時器開發(fā)工具 LMX2486 EVAL BOARD RoHS:否 制造商:Texas Instruments 產品:Evaluation Modules 類型:Clock Conditioners 工具用于評估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| LMX2486SQ | 制造商:Texas Instruments 功能描述:PLL Frequency Synthesizer Dual 5MHz to 4500MHz 24-Pin LLP EP T/R |

| LMX2486SQ/NOPB | 功能描述:鎖相環(huán) - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2486SQX | 制造商:Texas Instruments 功能描述:PLL Frequency Synthesizer Dual 5MHz to 4500MHz 24-Pin LLP EP T/R |

| LMX2486SQX/NOPB | 功能描述:鎖相環(huán) - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。