- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384592 > LF6197 (National Semiconductor Corporation) 160 ns Monolithic Sample-and-Hold Amplifier PDF資料下載

參數(shù)資料

| 型號(hào): | LF6197 |

| 廠(chǎng)商: | National Semiconductor Corporation |

| 元件分類(lèi): | 運(yùn)動(dòng)控制電子 |

| 英文描述: | 160 ns Monolithic Sample-and-Hold Amplifier |

| 中文描述: | 160納秒單片采樣保持放大器 |

| 文件頁(yè)數(shù): | 7/12頁(yè) |

| 文件大小: | 214K |

| 代理商: | LF6197 |

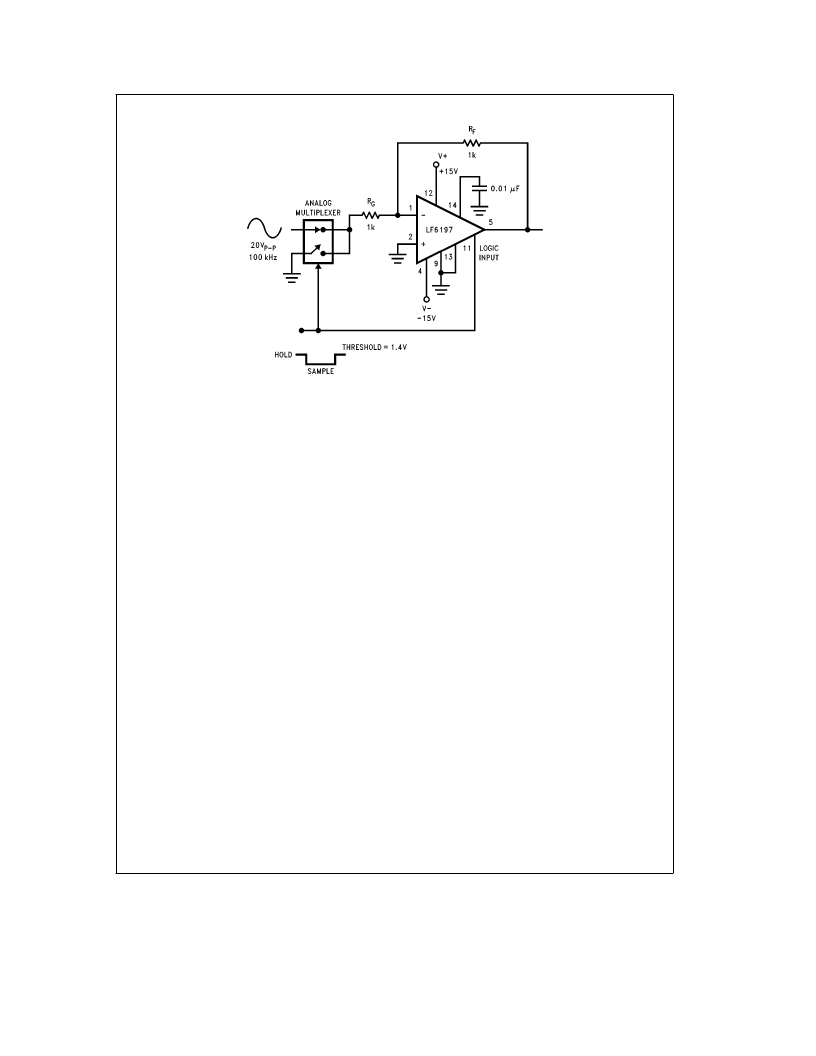

Test Circuit

TL/H/11381–4

FIGURE 1. Circuit configuration for the measurement of feedthrough attenuation. Input is connected

to ground in sample mode and is connected to 20 V

PP

, 100 kHz sine wave in hold mode.

Pin Descriptions

V

a

(12)

This is the positive power supply pin. A

a

5V to

a

15V supply voltage should be

applied to this pin and bypassed to

ground with a 0.1

m

F ceramic capacitor

in parallel with a 4.7

m

F tantalum capaci-

tor.

V

b

(4)

This is the negative power supply pin. A

b

5V to

b

15V supply voltage should be

applied to this pin and bypassed to

ground with a 0.1

m

F ceramic capacitor

in parallel with a 4.7

m

F tantalum capaci-

tor.

GND (9)

This is the ground reference pin. All sig-

nals are referenced to the potential at

this pin.

b

Input (1)

This is the inverting input of the ‘‘sam-

ple’’

amplifier.

Connecting

through a resistor to the output will con-

figure the sample-and-hold amplifier for

unity gain. Other inverting and non-in-

verting gains can be set by applying the

familiar op amp feedback topologies.

For stability reasons, stray capacitance

from the inverting input to ground should

be minimized.

this

pin

a

Input (2)

This is the non-inverting input of the

‘‘sample’’ amplifier. This pin should be

driven from a low impedance source.

Output (5)

This is the output of the sample-and-

hold amplifier.

LR1 (10)

This is the Logic Reference 1 input. By

applying the appropriate logic threshold

at this pin, the sample-and-hold amplifi-

er’s logic input can be made either CMOS

or ECL compatible. For TTL logic levels,

this pin should remain unconnected.

LR2 (13)

This is the Logic Reference 2 input. For

TTL logic levels, this pin should be con-

nected to ground; this sets the logic

threshold at the logic comparator’s invert-

ing pin at 1.4V. For CMOS or ECL logic

levels this pin should either remain un-

connected or connected to pin 10.

Logic Input (11)

This is the logic control input pin. A logic

low at this pin will configure the amplifier

in the ‘‘sample’’ mode while a logic high

will configure the amplifier in the ‘‘hold’’

mode. The TTL, CMOS, or ECL logic

compatibility will be determined by the

voltage threshold set at the logic compar-

ator’s inverting input.

Zener Reference For optimum acquisition and settling

Output (14)

times, this pin must be bypassed to

ground with a 0.01

m

F capacitor. Further-

more, for

g

5V supply operation, this pin

must be biased at 2.5V from a low imped-

ance source.

NC (3,6,7,8)

No connection.

7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LF6197CCJ | 160 ns Monolithic Sample-and-Hold Amplifier |

| LFCL-500-C-1 | Slide Switch; Circuitry:SPDT; Contact Current Max:4A; Switch Operation:On-On; Switch Terminals:Through Hole; Leaded Process Compatible:Yes; Mounting Type:PCB RoHS Compliant: Yes |

| LFCL500C3 | Cable Limiters |

| LFCL250A1 | Cable Limiters |

| LFCL250A3 | Cable Limiters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LF6197CCJ | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:160 ns Monolithic Sample-and-Hold Amplifier |

| LF6197J | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Sample/Track-and-Hold Amplifier |

| LF-65B | 制造商:SPC Multicomp 功能描述:FERRITE CORE HINGED 6.5MM 制造商:SPC Multicomp 功能描述:FERRITE CORE, SPLIT, 6.5MM, 220 OHM 制造商:SPC Multicomp 功能描述:FERRITE CORE, SPLIT, 6.5MM, 220 OHM/100MHZ, 300MHZ; Frequency Min:10MHz; Frequency Max:300MHz; Cable Diameter Max:6.5mm; External Depth:32mm; External Width:19.5mm; Ferrite Mounting:Cable; Frequency Range:10MHz to 300MHz; Series:LF ;RoHS Compliant: Yes |

| LF-65B | 制造商:KE KITAGAWA 功能描述:CORE HINGED 6.5MM |

| LF6BK | 功能描述:電纜組件 1/4 PATCHCORD 6 FT RoHS:否 制造商:Molex 產(chǎn)品:Power Assemblies 類(lèi)型:Cable Assembly 連接器端口 A:No Connector 連接器端口 A 管腳計(jì)數(shù):4 連接器端口 B:No Connector 連接器端口 B 管腳計(jì)數(shù): 型式:Male 線(xiàn)規(guī) - 美國(guó)線(xiàn)規(guī)(AWG):20, 28 長(zhǎng)度:0.305 m 顏色:Black, Red |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。