- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97995 > L6238SQA (STMICROELECTRONICS) BRUSHLESS DC MOTOR CONTROLLER, 5 A, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | L6238SQA |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 運動控制電子 |

| 英文描述: | BRUSHLESS DC MOTOR CONTROLLER, 5 A, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數(shù): | 31/31頁 |

| 文件大小: | 3465K |

| 代理商: | L6238SQA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁

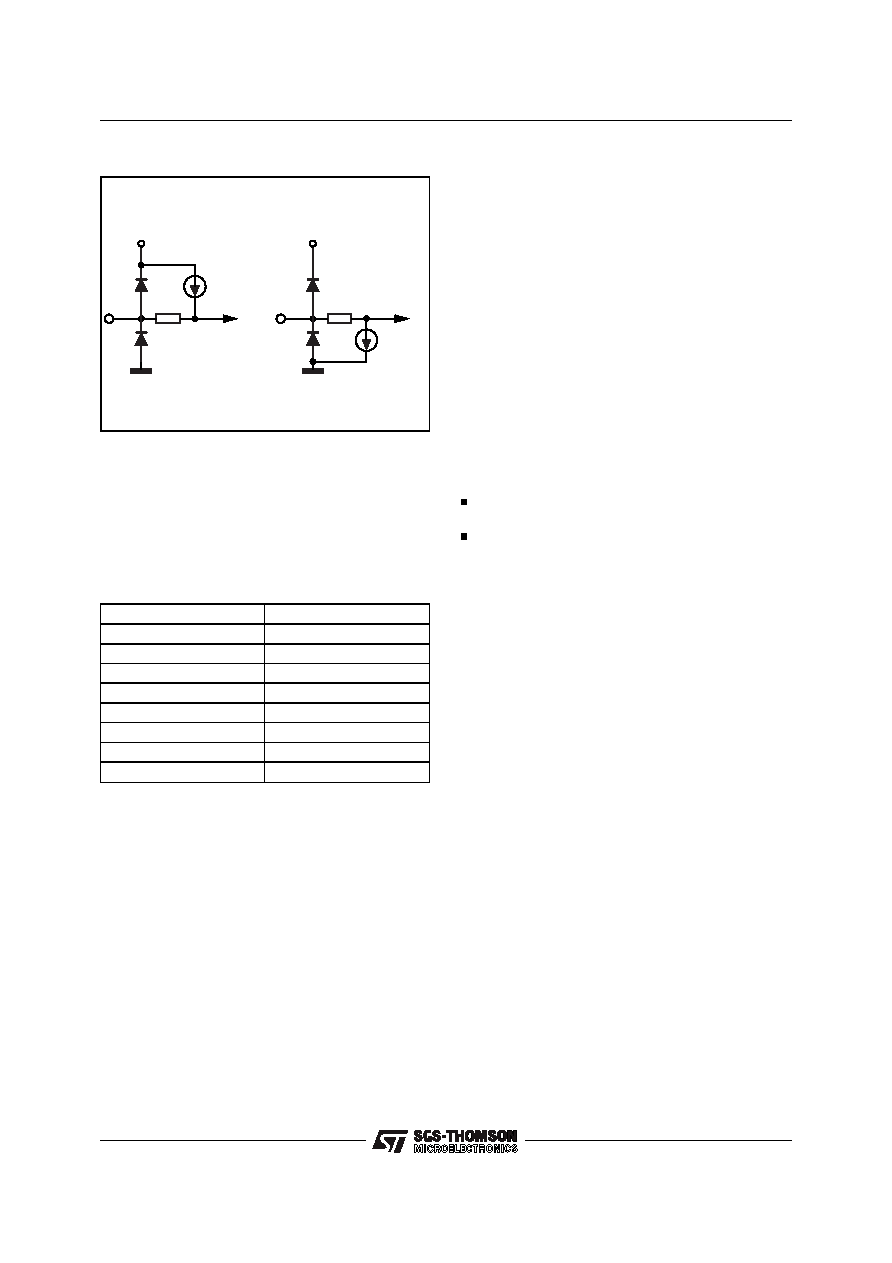

used in an application, it may either be connected

to ground or VLOGIC as required, It may also be

simply left unconnected.

If no connection is made, the pin is either pulled

high or low by internal constant current gener-

ators as shown above.

A listing of the logic and clock inputs is shown in

Table 1 with the corresponding default state.

1.3 Modes of Operation

There are 5 basic modes of operation.

1) Tristate

When Output Enable is low, the output power

drivers are tristated.

2) Start-Up

With Output Enable high, bringing Run/Brake

from a low to a high will energize the motor and

the system will be driven by the Fully-Integrated

StartUp Algorithm.

A user-defined Start-Up Algorithm, under control

of a MicroProcessor, can also be achieved via the

sequence increment input.

3) Run

Run mode is achieved when the motor speed

(controlled

by

the

external

microprocessor)

reaches the nominal speed.

4) Park

When Run/Brake is brought low, energy to park

the heads may be derived from the rectified Bemf.

The energy recovery time is a function of the

Brake Delay Time Constant. In this state, the qui-

escent current of the device is minimized (sleep

mode).

5) Brake

After the Energy Recovery Time-Out, the device

is in Brake, with all lower Drivers in full conduc-

tion.

There are two mutually exclusive conditions

which may be present during the Tristate Mode

(wake up):

a)the spindle is stopped.

b)the system is still running at a speed that

allows for resynchronization.

In order to minimize the ramp up time, the micro-

controller has the possibility to:

check the SPIN SENSE pin, (which toggles at

the Bemf zero crossing frequency)

enable the power to the motor based on the

previous information. Otherwise the

P may is-

sue a Brake command, followed by the start-

up procedure after the motor has stopped spin-

ning.

2.0 STATE DIAGRAMS

2.1 State Diagram

Figure 2-1 is a complete State Diagram of the

controller depicting the operational flow as a func-

tion of the control pins and motor status. The flow

can be separated into four distinct operations.

2.2 Align + Go

Figure 2-2 represent the normal flow that will

achieve a spin-up of the spindle motor using the

internally generated start up algorithm.

Upon

power

up,

or

from

any

state

with

Run/Brake low the controller first sets the state

machine for State=1 with the Outputs Tristated.

The period counter that monitors the time be-

tween zero crossing is stopped, analog with the

phase and mask delay counters.

When Run/Brake is brought high, the motor is in

the first part of the align mode at State 2 (Output

A high and Output C low). If Output Enable is

high, the controller first checks to determine if the

motor is still spinning for a time of 21

(with

Sys_Clk = 10MHz). The drivers are now enabled

and after the align time-out, (64/Falign), the se-

quencer double increments the outputs to State 4

(Output B high and Output A low). The first part

of this align mode is used to reduce the effects of

stiction

Pin Function

Configuration

Tdly (0,1,2)

Pull-Down

Select Pole

Pull-Down

PWM/Linear

Pull-Down

Output Enable

Pull-Down

Run/Brake

Pull-Up

Sequence Increment

Pull-Down

System Clock

Pull-Up

Faling

Pull-Up

Table 1

330

VLOGIC

10

A

330

VLOGIC

10

A

PULL-UP

PULL-DOWN

D95IN279

Figure 1-2

L6238S

9/31

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| L6238SQT | BRUSHLESS DC MOTOR CONTROLLER, 5 A, PQFP64 |

| L6238S013TR | BRUSHLESS DC MOTOR CONTROLLER, 5 A, PQCC44 |

| L6246 | VOICE COIL MOTOR CONTROLLER, 3 A, PQFP44 |

| L6258EA | STEPPER MOTOR CONTROLLER, 2 A, PDSO36 |

| L6268 | VOICE COIL MOTOR CONTROLLER, 2.1 A, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| L6238SQT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:12V SENSORLESS SPINDLE MOTOR CONTROLLER |

| L6239 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| L623C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:THYRISTOR MODULE|BRIDGE|HALF-CNTLD|CA|280V V(RRM)|46A I(T) |

| L623F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:THYRISTOR MODULE|BRIDGE|HALF-CNTLD|CA|280V V(RRM)|46A I(T) |

| L624 | 制造商:CRYDOM 制造商全稱:Crydom Inc., 功能描述:Power Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。