- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374284 > K4T51043QC-ZLE7 (SAMSUNG SEMICONDUCTOR CO. LTD.) 512Mb C-die DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號: | K4T51043QC-ZLE7 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512Mb C-die DDR2 SDRAM |

| 中文描述: | 葷的512Mb芯片DDR2內(nèi)存 |

| 文件頁數(shù): | 16/29頁 |

| 文件大小: | 629K |

| 代理商: | K4T51043QC-ZLE7 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

Page 16 of 29

Rev. 1.4 Aug. 2005

DDR2 SDRAM

512Mb C-die DDR2 SDRAM

Notes :

1. IDD specifications are tested after the device is properly initialized

2. Input slew rate is specified by AC Parametric Test Condition

3. IDD parameters are specified with ODT disabled.

4. Data bus consists of DQ, DM, DQS, DQS\, RDQS, RDQS\, LDQS, LDQS\, UDQS, and UDQS\. IDD values must be met with all combinations of EMRS

bits 10 and 11.

5. Definitions for IDD

LOW is defined as Vin

≤

VILAC(max)

HIGH is defined as Vin

≥

VIHAC(min)

STABLE is defined as inputs stable at a HIGH or LOW level

FLOATING is defined as inputs at VREF = VDDQ/2

SWITCHING is defined as:

inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and control

signals, and

inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including

masks or strobes.

For purposes of IDD testing, the following parameters are utilized

Detailed IDD7

The detailed timings are shown below for IDD7.

Legend: A = Active; RA = Read with Autoprecharge; D = Deselect

IDD7: Operating Current: All Bank Interleave Read operation

All banks are being interleaved at minimum tRC(IDD) without violating tRRD(IDD) and tFAW(IDD) using a burst length of 4. Control and address bus

inputs are STABLE during DESELECTs. IOUT = 0mA

Timing Patterns for 4 bank devices with 1KB or 2KB page size

-DDR2-400 3/3/3

A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D D

-DDR2-533 4/4/4

A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D D D

-DDR2-667 5/5/5

A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D D

-DDR2-800 5/5/5

A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D D D D D

DDR2-800

DDR2-667

DDR2-533

DDR2-400

Units

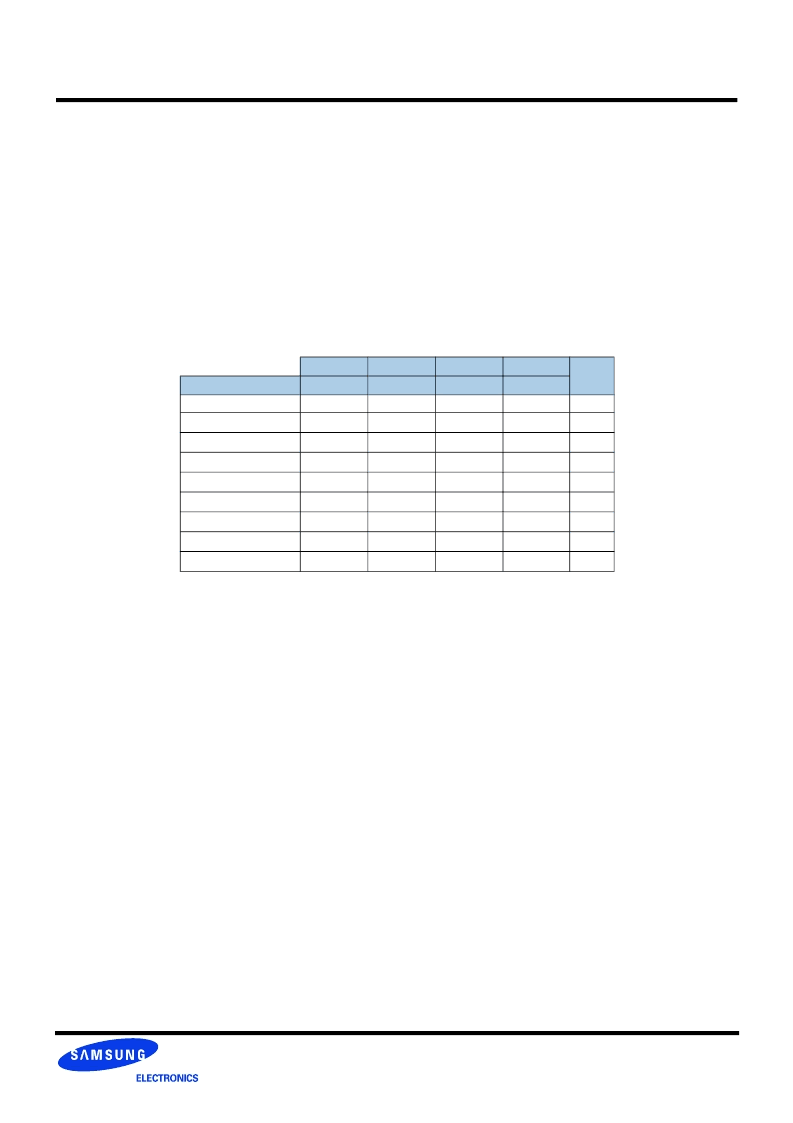

Parameter

5-5-5

5-5-5

4-4-4

3-3-3

CL(IDD)

5

5

4

3

tCK

tRCD(IDD)

12.5

15

15

15

ns

tRC(IDD)

57.5

60

60

55

ns

tRRD(IDD)-x4/x8

7.5

7.5

7.5

7.5

ns

tRRD(IDD)-x16

10

10

10

10

ns

tCK(IDD)

2.5

3

3.75

5

ns

tRASmin(IDD)

45

45

45

40

ns

tRP(IDD)

12.5

15

15

15

ns

tRFC(IDD)

105

105

105

105

ns

相關PDF資料 |

PDF描述 |

|---|---|

| K4T51043QC-ZCLE6 | 512Mb C-die DDR2 SDRAM |

| K4T51043QC-ZCD5 | 512Mb C-die DDR2 SDRAM |

| K4 | KS SERIES KEY SWITCHES |

| K5-C | Adjustable Type Coils |

| K5-N | Adjustable Type Coils |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4T51043QE | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb E-die DDR2 SDRAM Specification |

| K4T51043QG | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb G-die DDR2 SDRAM Specification |

| K4T51043QG-HCLCC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb G-die DDR2 SDRAM Specification |

| K4T51043QG-HCLD5 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb G-die DDR2 SDRAM Specification |

| K4T51043QG-HCLE6 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb G-die DDR2 SDRAM Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復。