- 您現在的位置:買賣IC網 > PDF目錄374283 > K4S643232C-TC10 (SAMSUNG SEMICONDUCTOR CO. LTD.) Low Noise Precision Advanced LinCMOS(TM) Single Operational Amplifier 20-LCCC -55 to 125 PDF資料下載

參數資料

| 型號: | K4S643232C-TC10 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | Low Noise Precision Advanced LinCMOS(TM) Single Operational Amplifier 20-LCCC -55 to 125 |

| 中文描述: | 200萬× 32內存為512k × 32 × 4銀行同步DRAM LVTTL |

| 文件頁數: | 8/43頁 |

| 文件大小: | 1155K |

| 代理商: | K4S643232C-TC10 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

K4S643232C

CMOS SDRAM

REV. 1.1 Nov. '99

- 8 -

1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf)=1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

Note :

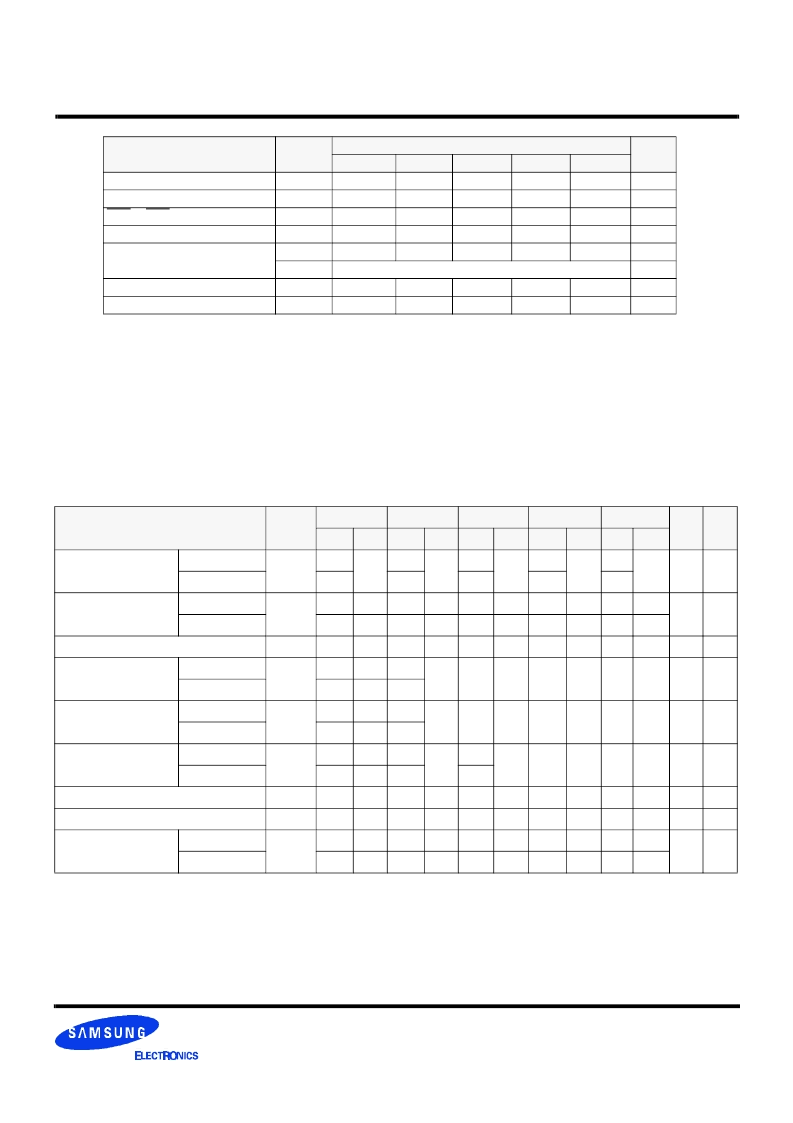

AC CHARACTERISTICS

(AC operating conditions unless otherwise noted)

Parameter

Symbol

-55

-60

-70

-80

-10

Unit

Note

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

CLK cycle time

CAS Latency=3

t

CC

5.5

1000

6

1000

7

1000

8

1000

10

1000

ns

1

CAS Latency=2

-

-

-

10

12

CLK to valid

output delay

CAS Latency=3

t

SAC

-

5

-

5.5

-

5.5

-

6

-

6

ns

1, 2

CAS Latency=2

-

-

-

-

-

-

-

6

-

8

Output data

t

OH

2

-

2.5

-

2.5

-

2.5

-

2.5

-

ns

2

CLK high pulse width

CAS Latency=3

t

CH

2

-

2.5

-

3

-

3

-

3.5

-

ns

3

CAS Latency=2

-

-

-

CLK low pulse width

CAS Latency=3

t

CL

2

-

2.5

-

3

-

3

-

3.5

-

ns

3

CAS Latency=2

-

-

-

Input setup time

CAS Latency=3

t

SS

1.5

-

1.5

-

1.75

-

2

-

2.5

-

ns

3

CAS Latency=2

-

-

-

-

Input hold time

t

SH

1

-

1

-

1

-

1

-

1

-

ns

3

CLK to output in Low-Z

t

SLZ

1

-

1

-

1

-

1

-

1

-

ns

2

CLK to output

in Hi-Z

CAS Latency=3

t

SHZ

-

5

-

5.5

-

5.5

-

6

-

6

ns

CAS Latency=2

-

-

-

-

-

-

-

6

-

8

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. For -55/60/70/80/10, tRDL=1CLK product can be supported within restricted amounts and it will be distinguished by bucket

code "NV". From the next generation, tRDL will be only 2CLK for every clock frequency.

6. A new command should be issued after self refersh exit followed by tRFC.

Parameter

Symbol

Version

-70

7

14

21

21

49

100

70

70

Unit

-55

5.5

11

16.5

16.5

38.5

-60

6

12

18

18

42

-80

8

16

20

20

48

-10

10

20

20

20

48

CLK cycle time

Row active to row active delay

RAS to CAS delay

Row precharge time

t

CC(min)

t

RRD(min)

t

RCD(min)

t

RP(min)

t

RAS(min)

t

RAS(max)

t

RC

(

min

)

t

RFC

(

min

)

ns

ns

ns

ns

ns

us

ns

ns

Row active time

Row cycle time

Row cycle time in Auto refresh

55

66

60

72

70

70

70

70

相關PDF資料 |

PDF描述 |

|---|---|

| K4S643232C-TC55 | Low Noise Precision Advanced LinCMOS(TM) Single Operational Amplifier 8-CDIP -55 to 125 |

| K4S643232C-TC60 | Low Noise Precision Advanced LinCMOS(TM) Single Operational Amplifier 20-LCCC -55 to 125 |

| K4S643232C-TC70 | Low Noise Precision Advanced LinCMOS(TM) Single Operational Amplifier 8-CDIP -55 to 125 |

| K4S643232E | 2M x 32 SDRAM 512K x 32bit x 4 Banks Synchronous DRAM LVTTL |

| K4S643232E-TE70 | 2M x 32 SDRAM 512K x 32bit x 4 Banks Synchronous DRAM LVTTL(3.3V) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| K4S643232C-TC55 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 32 SDRAM 512K x 32bit x 4 Banks Synchronous DRAM LVTTL |

| K4S643232C-TC60 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 32 SDRAM 512K x 32bit x 4 Banks Synchronous DRAM LVTTL |

| K4S643232CTC70 | 制造商:Samsung Semiconductor 功能描述: |

| K4S643232C-TC70 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 32 SDRAM 512K x 32bit x 4 Banks Synchronous DRAM LVTTL |

| K4S643232C-TC70000 | 制造商:Samsung SDI 功能描述:DRAM Chip SDRAM 64M-Bit 2Mx32 3.3V 86-Pin TSOP-II Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。