- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373066 > K4S281632B-N (SAMSUNG SEMICONDUCTOR CO. LTD.) 2M x 16Bit x 4 Banks Synchronous DRAM in sTSOP PDF資料下載

參數(shù)資料

| 型號: | K4S281632B-N |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 2M x 16Bit x 4 Banks Synchronous DRAM in sTSOP |

| 中文描述: | 200萬× 16 × 4銀行同步DRAM在sTSOP |

| 文件頁數(shù): | 11/14頁 |

| 文件大小: | 145K |

| 代理商: | K4S281632B-N |

SDRAM 128Mb E-die (x4, x8, x16)

CMOS SDRAM

Rev. 1.4 February. 2004

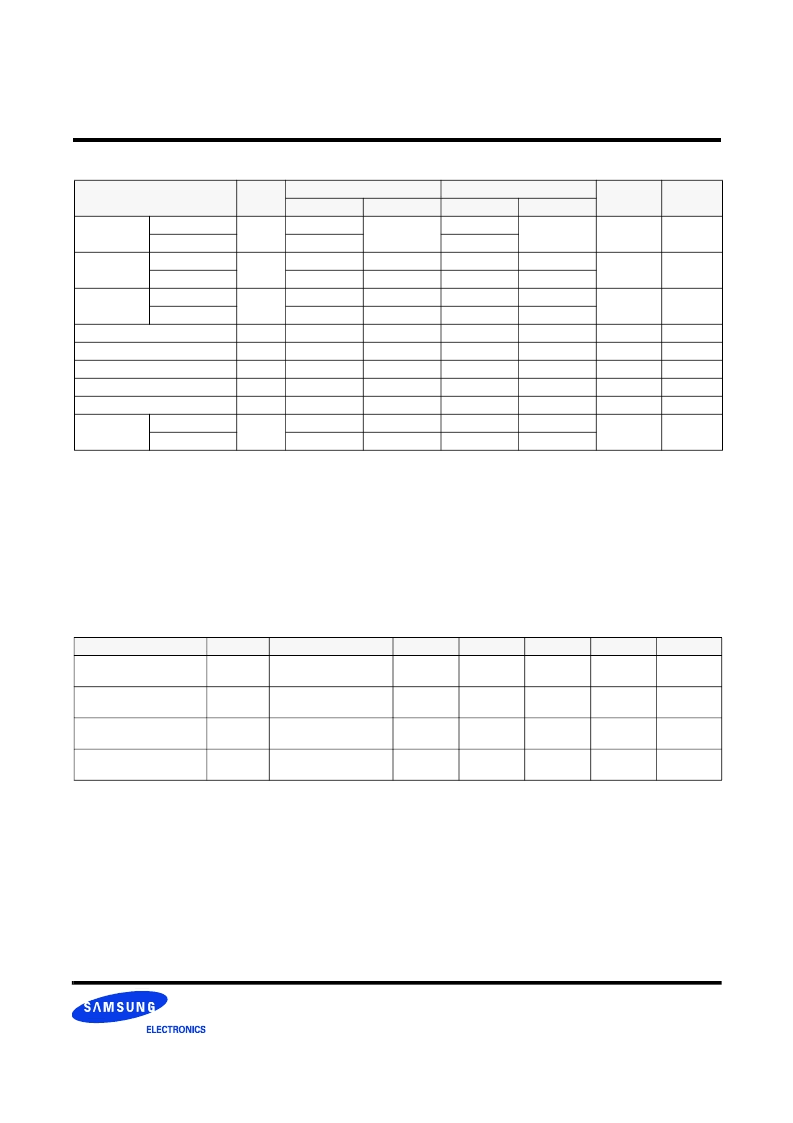

DQ BUFFER OUTPUT DRIVE CHARACTERISTICS

Parameter

Symbol

Condition

Min

Typ

Max

Unit

Notes

Output rise time

trh

Measure in linear

region : 1.2V ~ 1.8V

Measure in linear

region : 1.2V ~ 1.8V

Measure in linear

region : 1.2V ~ 1.8V

Measure in linear

region : 1.2V ~ 1.8V

1.37

4.37

Volts/ns

3

Output fall time

tfh

1.30

3.8

Volts/ns

3

Output rise time

trh

2.8

3.9

5.6

Volts/ns

1,2

Output fall time

tfh

2.0

2.9

5.0

Volts/ns

1,2

1. Rise time specification based on 0pF + 50

to V

SS

, use these values to design to.

2. Fall time specification based on 0pF + 50

to V

DD

, use these values to design to.

3. Measured into 50pF only, use these values to characterize to.

4. All measurements done with respect to V

SS

.

Notes :

1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

Notes :

AC CHARACTERISTICS

(AC operating conditions unless otherwise noted)

Parameter

Symbol

- 60 (x16 only)

Min

6

-

- 75

Unit

Note

Max

Min

7.5

10

Max

CLK cycle

time

CAS latency=3

CAS latency=2

CAS latency=3

CAS latency=2

CAS latency=3

CAS latency=2

t

CC

1000

1000

ns

1

CLK to valid

output delay

t

SAC

5

-

5.4

6

ns

1,2

Output data

hold time

t

OH

2.5

-

2.5

2.5

1.5

1.0

1

3

3

ns

2

CLK high pulse width

CLK low pulse width

Input setup time

Input hold time

CLK to output in Low-Z

t

CH

t

CL

t

SS

t

SH

t

SLZ

2.5

2.5

1.5

0.8

1

ns

ns

ns

ns

ns

3

3

3

3

2

CLK to output

in Hi-Z

CAS latency=3

CAS latency=2

t

SHZ

5

-

5.4

6

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4S280432E | 128Mb E-die SDRAM Specification |

| K4S280432E-TC75 | 128Mb E-die SDRAM Specification |

| K4S280832F-TC75 | RES, 16.9, 1/16W, TKF, 1%, 0603 |

| K4S280832F-TCL75 | 128Mb F-die SDRAM Specification |

| K4S280832F-UL75 | 128Mb F-die SDRAM Specification 54 TSOP-II with Pb-Free (RoHS compliant) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4S281632B-NC/L1H | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 16Bit x 4 Banks Synchronous DRAM in sTSOP |

| K4S281632B-NC/L1L | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 16Bit x 4 Banks Synchronous DRAM in sTSOP |

| K4S281632B-TC10 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mbit SDRAM 2M x 16Bit x 4 Banks Synchronous DRAM LVTTL |

| K4S281632B-TC1H | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mbit SDRAM 2M x 16Bit x 4 Banks Synchronous DRAM LVTTL |

| K4S281632B-TC1L | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mbit SDRAM 2M x 16Bit x 4 Banks Synchronous DRAM LVTTL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。