- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄360749 > ICS503MT LOCO⑩ PLL Clock Multiplier PDF資料下載

參數(shù)資料

| 型號(hào): | ICS503MT |

| 英文描述: | LOCO⑩ PLL Clock Multiplier |

| 中文描述: | 本地⑩PLL時(shí)鐘乘法器 |

| 文件頁(yè)數(shù): | 3/4頁(yè) |

| 文件大小: | 60K |

| 代理商: | ICS503MT |

ICS503

LOCO PLL Clock Multiplier

MDS 503 A

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA95126(408) 295-9800tel www.icst.com

3

Revision 111000

PRELIMINARY INFORMATION

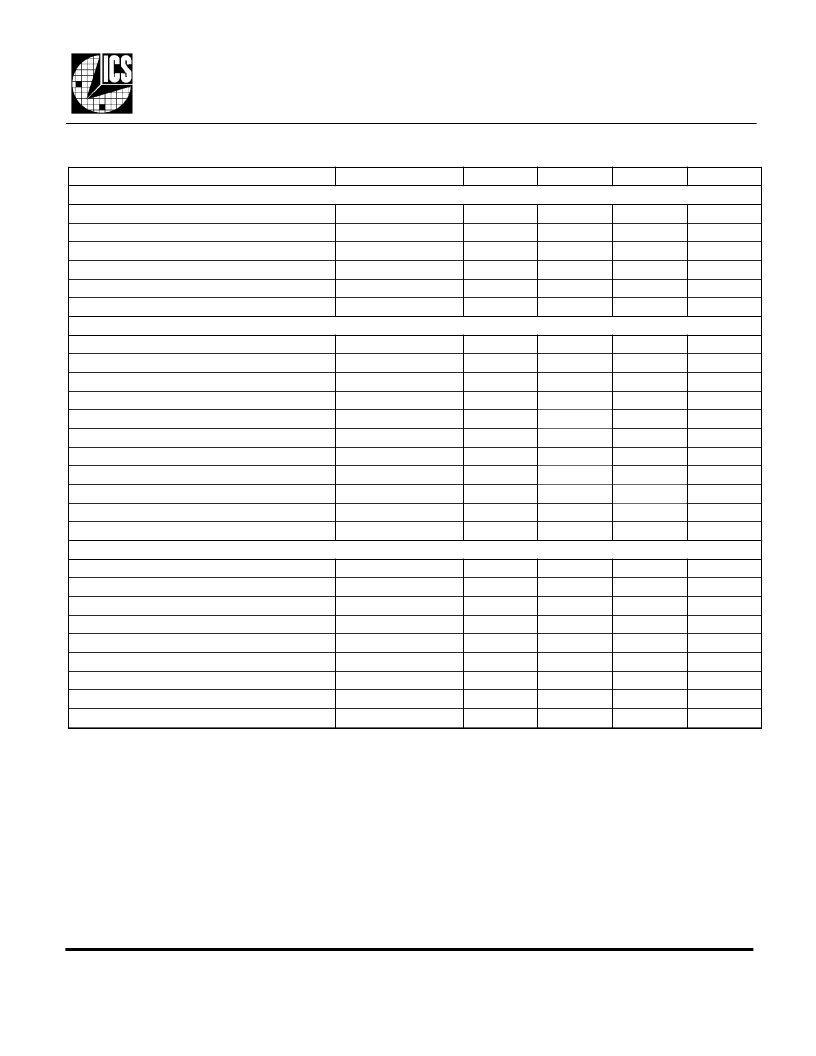

Parameter

ABSOLUTE MAXIMUM RATINGS (stresses beyond these can permanently damage the device)

Supply Voltage, VDD

Inputs

Clock Output

Ambient Operating Temperature

Soldering Temperature

Storage temperature

DC CHARACTERISTICS (VDD = 5.0V unless otherwise noted)

Operating Voltage, VDD

Input High Voltage, VIH, ICLK only

Input Low Voltage, VIL, ICLK only

Input High Voltage, VIH

Input Low Voltage, VIL

Output High Voltage, VOH, CMOS high

Output High Voltage, VOH

Output Low Voltage, VOL

IDD Operating Supply Current, 14 MHz crystal No Load, 80MHz

Short Circuit Current

Input Capacitance, S1, S0

AC CHARACTERISTICS (VDD = 5.0V unless otherwise noted)

Input Frequency, crystal input

Input Frequency, clock input

Output Frequency

Output Frequency

Output Clock Rise Time

Output Clock Fall Time

Output Clock Duty Cycle

Absolute Clock Period Jitter

One Sigma Clock Period Jitter

Conditions

Minimum

Typical

Maximum

Units

Referenced to GND

Referenced to GND

Referenced to GND

7

V

V

V

°C

°C

°C

-0.5

-0.5

0

VDD+0.5

VDD+0.5

70

260

150

Max of 10 seconds

-65

3

5.5

V

V

V

V

V

V

V

V

ICLK (Pin 1)

ICLK (Pin 1)

S1, S0

S1, S0

IOH=-4mA

IOH=-25mA

IOL=25mA

(VDD/2)+1

VDD/2

VDD/2

(VDD/2)-1

VDD-0.5

0.5

VDD-0.4

2.4

0.4

16

±70

4

mA

mA

pF

CLK output

Pins 6, 7

See table on page 2

See table on page 2

VDD = 4.5 to 5.5V

VDD = 3.0 to 3.6V

0.8 to 2.0V

2.0 to 0.8V

at VDD/2

Deviation from mean

5

2

14

14

27

50

160

100

55

MHz

MHz

MHz

MHz

ns

ns

%

ps

ps

1

1

45

49 to 51

±120

50

Electrical Specifications

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS504M | Industrial Control IC |

| ICS504MT | Industrial Control IC |

| ICS511 | FIBER OPTIC TRANSMITTER,5MBD,BLUE |

| ICS511-DPK | XCMR 600NM HORIZ 1MBD GRAY |

| ICS511-DWF | FIBERTHT XCMR 600NM HORIZ 40KB BLACK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS504M | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Industrial Control IC |

| ICS504MT | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Industrial Control IC |

| ICS507-01 | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:PECL Clock Synthesizer |

| ICS507-01-DPK | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:PECL Clock Synthesizer |

| ICS507-01-DSW | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:PECL Clock Synthesizer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。