- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370810 > HYS6472V4200GU (SIEMENS AG) Network Cable Assembly; Connector Type A:T568A/B Modular Plug; Connector Type B:T568A/B Modular Plug; Cable Length:25ft; Approval Categories:Augmented Category 6 standards; cord color per TIA/EIA-606 standard RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號(hào): | HYS6472V4200GU |

| 廠商: | SIEMENS AG |

| 英文描述: | Network Cable Assembly; Connector Type A:T568A/B Modular Plug; Connector Type B:T568A/B Modular Plug; Cable Length:25ft; Approval Categories:Augmented Category 6 standards; cord color per TIA/EIA-606 standard RoHS Compliant: Yes |

| 中文描述: | 3.3 4米× 64/72-Bit一銀行內(nèi)存模塊3.3 8米× 64/72-Bit 2銀行內(nèi)存模塊 |

| 文件頁數(shù): | 11/15頁 |

| 文件大小: | 76K |

| 代理商: | HYS6472V4200GU |

HYS64(72)V4200/8220GU

SDRAM-Modules

Semiconductor Group

11

A serial presence detect storage device - E

2

PROM - is assembled onto the module. Information about the module

configuration, speed, etc. is written into the E

2

PROM device during module production using a serial presence

detect protocol ( I

2

C synchronous 2-wire bus)

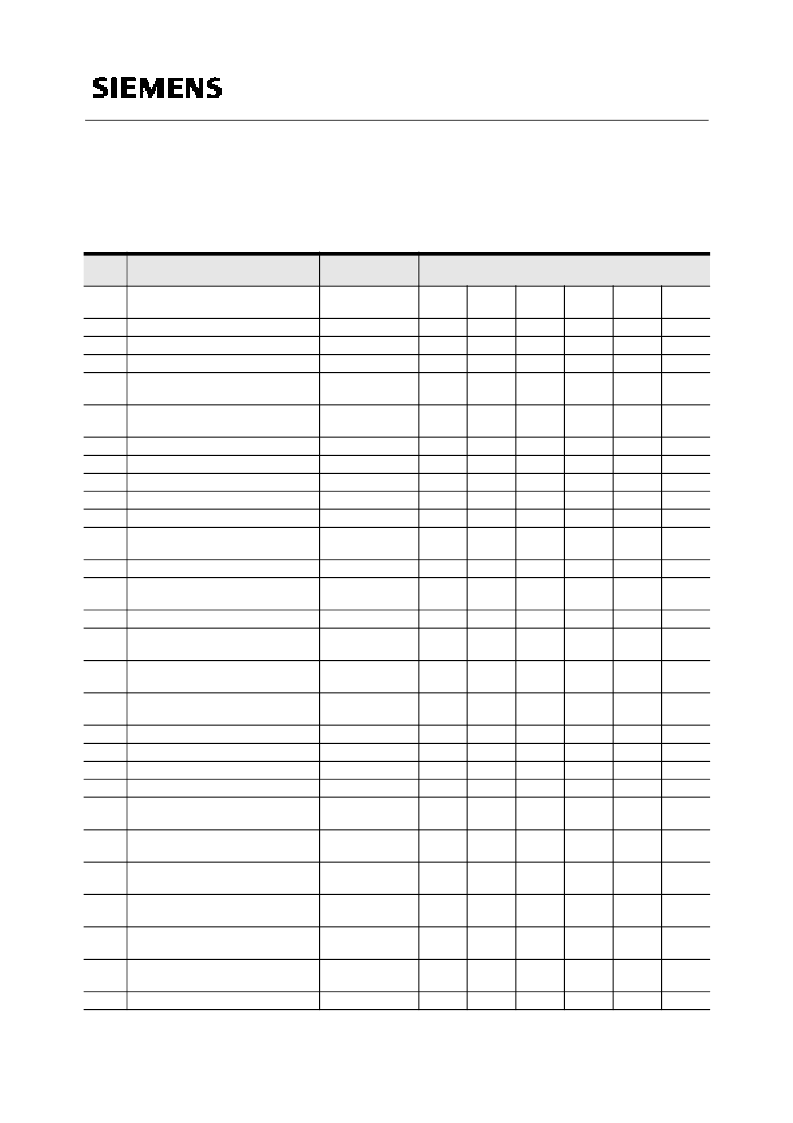

SPD-Table for PC100 modules:

Byte#

Description

SPD Entry

Value

Hex

4Mx64

-8

80

08

04

0C

4Mx64

-8B

80

08

04

0C

4Mx72

-8

80

08

04

0C

8Mx64

-8

80

08

04

0C

8Mx64

-8B

80

08

04

0C

8Mx72

-8

80

08

04

0C

0

1

2

3

Number of SPD bytes

Total bytes in Serial PD

Memory Type

Number of Row Addresses (wit-

hout BS bits)

Number of Column Addresses

(for 16 SDRAM)

Number of DIMM Banks

Module Data Width

Module Data Width (cont’d)

Module Interface Levels

SDRAM Cycle Time at CL=3

SDRAM Access time from Clock

at CL=3

Dimm Config (Error Det/Corr.)

Refresh Rate/Type

128

256

SDRAM

12

4

8

08

08

08

08

08

08

5

6

7

8

9

1 / 2

64

0

LVTTL

10.0 ns

6.0 ns

01

40

00

01

A0

60

01

40

00

01

A0

60

01

48

00

01

A0

60

02

40

00

01

A0

60

02

40

00

01

A0

60

02

48

00

01

A0

60

10

11

12

none

00

80

00

80

02

80

00

80

00

80

02

80

Self-Refresh,

15.6

μ

s

x16

n/a / x8

13

14

SDRAM width, Primary

Error Checking SDRAM data

width

Minimum clock delay for back-to-

back random column address

Burst Length supported

10

00

10

00

10

08

10

00

10

00

10

08

15

t

ccd

= 1 CLK

01

01

01

01

01

01

16

1, 2, 4, 8 & full

page

4

CL = 2 & 3

CS latency = 0

WL = 0

non buffered/

non reg.

Vcc tol +/- 10%

8F

8F

8F

8F

8F

8F

17

18

19

20

21

Number of SDRAM banks

Supported CAS Latencies

CS Latencies

WE Latencies

SDRAM DIMM module attributes

04

06

01

01

00

04

06

01

01

00

04

06

01

01

00

04

06

01

01

00

04

06

01

01

00

04

06

01

01

00

22

SDRAM Device Attributes :Gene-

ral

Minimum Clock Cycle Time at

CAS Latency = 2

Maximum data access time from

Clock for CL=2

Minimum Clock Cycle Time at CL

= 1

Maximum Data Access Time

from Clock at CL=1

Minimum Row Precharge Time

06

06

06

06

06

06

23

10.0 / 12.0ns

A0

C0

A0

A0

C0

A0

24

6.0 / 7.0ns

60

70

60

60

70

60

25

not supported

FF

FF

FF

FF

FF

FF

26

not supported

FF

FF

FF

FF

FF

FF

27

20 / 30 ns

14

1E

14

14

1E

14

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS64V4200GU-8 | 3.3V 4M x 64/72-Bit 1 BANK SDRAM Module 3.3V 8M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V4200GU-8B | 3.3V 4M x 64/72-Bit 1 BANK SDRAM Module 3.3V 8M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V8220GU-8 | 3.3V 4M x 64/72-Bit 1 BANK SDRAM Module 3.3V 8M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V8220GU-8B | 3.3V 4M x 64/72-Bit 1 BANK SDRAM Module 3.3V 8M x 64/72-Bit 2 BANK SDRAM Module |

| HYS72V64220GU-75-C2 | 3.3 V 64M x 64/72-Bit, 512MByte SDRAM Modules 168-pin Unbuffered DIMM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS64-74V8200GU | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:3.3 V 8M x 64/72-Bit 1 Bank SDRAM Module 3.3 V 16M x 64/72-Bit 2 Bank SDRAM Module |

| HYS64D128020GBDL-7-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:?1GB (1024Mx64) PC2100 2-bank? |

| HYS64D128020GU-7-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.5 V 184-pin Unbuffered DDR-I SDRAM Modules |

| HYS64D128020GU-8-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.5 V 184-pin Unbuffered DDR-I SDRAM Modules |

| HYS64D128021 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:200-Pin Small Outline Dual-In-Line Memory Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。