- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370795 > HYE25L256160AC (INFINEON TECHNOLOGIES AG) 256-Mbit Mobile-RAM PDF資料下載

參數(shù)資料

| 型號: | HYE25L256160AC |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 256-Mbit Mobile-RAM |

| 中文描述: | 256兆移動RAM |

| 文件頁數(shù): | 21/55頁 |

| 文件大?。?/td> | 1053K |

| 代理商: | HYE25L256160AC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

3

3

8

8

9.5

–

–

–

0.5

Data Sheet

21

V1.1, 2003-04-16

HYE25L256160AC

256-Mbit Mobile-RAM

Electrical Characteristics

4.2

Timing Characteristics

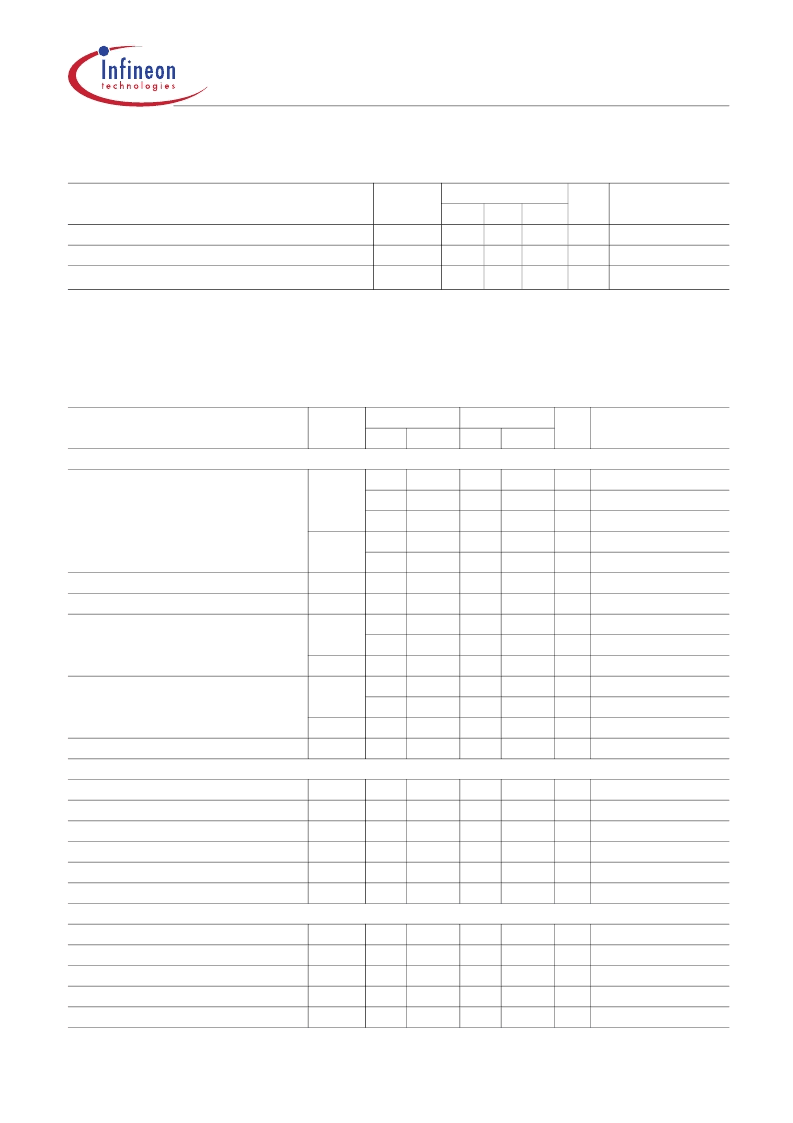

Table 9

Parameter

Input and Output Capacitances

Symbol

Values

typ.

–

–

–

Unit

Note/

Test Condition

min.

–

–

4.0

max.

3.5

3.8

5.0

Input Capacitance: CLK

Input Capacitance: All other input-only pins

Input/Output Capacitance: DQ

C

I1

C

I2

C

IO

pF

pF

pF

1)

1) These values are guaranteed by design and are tested on a sample base only.

V

DDQ

=

V

DD

= 2.5 V

±

0.2 V,

f

= 1 MHz,

T

CASE

= 25

°

C,

V

OUT(DC)

=

V

DDQ

/2,

V

OUT

(Peak to Peak) 0.2 V. Unused pins are tied to ground.

1)

1)

Table 10

Parameter

AC Timing Characteristics

1)2)

Symbol

–8

max.

–7.5

max.

Unit Note/ Test Condition

min.

min.

Clock

DQ output access time from CLK

t

AC3

–

–

–

–

–

7.5

6

6

7.5

6

–

–

–

–

–

125

125

105

1.5

–

–

–

–

–

2.5

2.5

7.5

8

9.5

–

–

–

0.3

7.5

6

5.4

7.5

6

–

–

–

–

–

133

125

105

1.2

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

V

DDQ

≥

2.3 V

3)

MHz

V

DDQ

< 2.3 V

3)

MHz

ns

–

V

DDQ

< 2.3 V

3)4)5)8)

V

DDQ

≥

2.3 V

3)4)5)8)

V

DDQ

≥

3.0 V

3)4)5)8)

V

DDQ

< 2.3 V

3)4)5)8)

V

DDQ

≥

2.3 V

3)4)5)8)

–

–

V

DDQ

≥

2.3 V

3)

V

DDQ

< 2.3 V

3)

3)

t

AC2

CK high-level width

CK low-level width

Clock cycle time

t

CH

t

CL

t

CK3

t

CK2

f

CK3

Clock frequency

f

CK2

t

T

3)

Transition time

Setup and Hold Times

Input setup time

Input hold time

CKE setup time

CKE hold time

Mode register setup time

Power down moder entry time

Common Parameters

Active to Read or Write delay

Precharge command period

Active to Precharge command

Active bank A to Active bank A period

Active bank A to Active bank B delay

t

IS

t

IH

t

CKS

t

CKH

t

RSC

t

SB

2

1

2

1

2

0

–

–

–

–

–

8

1.5

0.8

1.5

0.8

2

0

–

–

–

–

–

7.5

ns

ns

ns

ns

t

CK

ns

6)

6)

6)

6)

–

–

t

RCD

t

RP

t

RAS

t

RC

t

RRD

19

19

48

70

16

–

–

100000 45

–

–

19

19

–

–

100000 ns

–

–

ns

ns

7)

7)

7)

67

15

ns

ns

7)

7)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYE25L256160AC-8 | 256-Mbit Mobile-RAM |

| HYE25L256160AF | 256MBit Mobile-RAM |

| HYE25L256160AF-75 | CAP TANT 10UF 6.3V 20% SMD |

| HYE25L256160AC-7.5 | BJAWBMSpecialty DRAMs Mobile-RAM |

| HYM321000GS-60 | 1M x 32-Bit Dynamic RAM Module 2M x 16-Bit Dynamic RAM Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYE25L256160AC-7.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:BJAWBMSpecialty DRAMs Mobile-RAM |

| HYE25L256160AC-75 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:256-Mbit Mobile-RAM |

| HYE25L256160AC-8 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:256-Mbit Mobile-RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。