- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224000 > HYB18T1G800C4F-3 (QIMONDA AG) 128M X 8 DDR DRAM, 0.45 ns, PBGA60 PDF資料下載

參數(shù)資料

| 型號: | HYB18T1G800C4F-3 |

| 廠商: | QIMONDA AG |

| 元件分類: | DRAM |

| 英文描述: | 128M X 8 DDR DRAM, 0.45 ns, PBGA60 |

| 封裝: | GREEN, PLASTIC, TFBGA-60 |

| 文件頁數(shù): | 46/58頁 |

| 文件大?。?/td> | 1898K |

| 代理商: | HYB18T1G800C4F-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

HYB18T1G[40/80/16]0C4F

1-Gbit Double-Data-Rate-Two SDRAM

Internet Data Sheet

Rev. 1.01, 2008-11

50

04212008-66HT-ZLFE

7.4

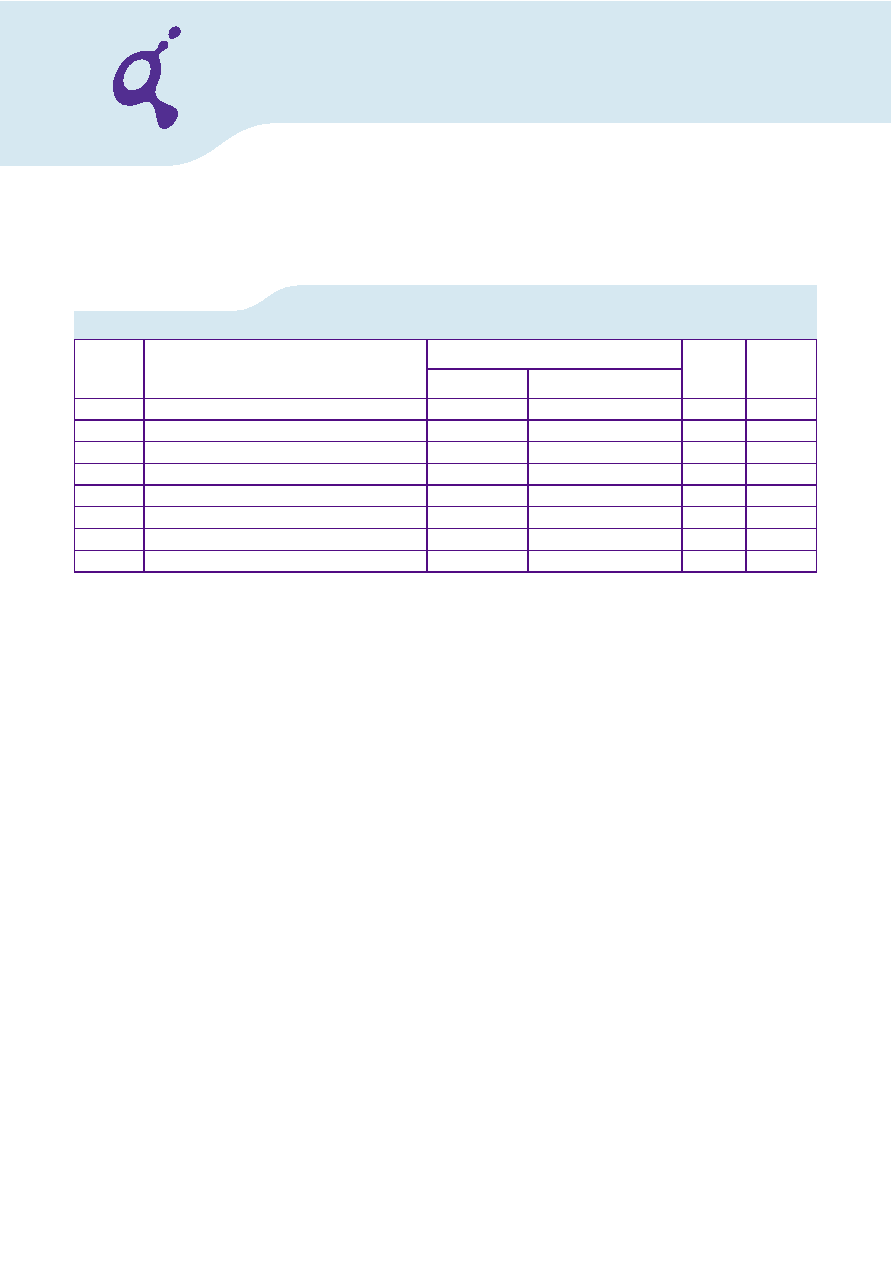

ODT AC Electrical Characteristics

This chapter describes the ODT AC electrical characteristics.

TABLE 41

ODT AC Characteristics and Operating Conditions for DDR2–667 and DDR2–800

Symbol

Parameter / Condition

Values

Unit

Note

Min.

Max.

t

AOND

ODT turn-on delay

2

n

CK

1)

1) New units, “

t

CK.AVG” and “nCK”, are introduced in DDR2-667 and DDR2-800 Unit “tCK.AVG” represents the actual tCK.AVG of the input clock

under operation. Unit “

n

CK” represents one clock cycle of the input clock, counting the actual clock edges. Note that in DDR2-400 and

DDR2-533, “

t

CK” is used for both concepts. Example: tXP = 2 [nCK] means; if Power Down exit is registered at Tm, an Active command may

be registered at

T

m + 2, even if (Tm + 2 - Tm) is 2 x tCK.AVG + tERR.2PER.MIN.

t

AON

ODT turn-on

t

AC.MIN

t

AC.MAX +0.7

ns

2) ODT turn on time min is when the device leaves high impedance and ODT resistance begins to turn on. ODT turn on time max is when

the ODT resistance is fully on. Both are measured from

t

AOND, which is interpreted differently per speed bin. For DDR2-667/800 tAOND is

2 clock cycles after the clock edge that registered a first ODT HIGH counting the actual input clock edges.

t

AONPD

ODT turn-on (Power-Down Modes)

t

AC.MIN +2

2

t

CK + tAC.MAX +1

ns

t

AOFD

ODT turn-off delay

2.5

n

CK

t

AOF

ODT turn-off

t

AC.MIN

t

AC.MAX +0.6

ns

3) ODT turn off time min is when the device starts to turn off ODT resistance. ODT turn off time max is when the bus is in high impedance.

Both are measured from

t

AOFD, which is interpreted differently per speed bin. For DDR2-667/800, if tCK.AVG = 3 ns is assumed,

t

AOFD is 1.5 ns (= 0.5 x 3 ns) after the second trailing clock edge counting from the clock edge that registered a first ODT LOW and by

counting the actual input clock edges.

t

AOFPD

ODT turn-off (Power-Down Modes)

t

AC.MIN + 2

2.5

t

CK + tAC.MAX +1

ns

t

ANPD

ODT to Power Down Mode Entry Latency

3

—

n

CK

t

AXPD

ODT Power Down Exit Latency

8

—

n

CK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB3165800AJ-40 | 8M X 8 FAST PAGE DRAM, 40 ns, PDSO32 |

| HYB39S64400AT-8 | 16M X 4 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| HYC532410-50 | 4M X 32 MULTI DEVICE DRAM CARD, 50 ns, XMA88 |

| HYE18M256320CF-7.5 | 8M X 32 DDR DRAM, 6 ns, PBGA90 |

| HYM564124AR-60 | 1M X 64 EDO DRAM MODULE, DMA168 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T256400AF-3.7 | 制造商:Infineon Technologies AG 功能描述:64M X 4 DDR DRAM, 0.5 ns, PBGA60 |

| HYB18T256400AF-5 | 制造商:Infineon Technologies AG 功能描述:SDRAM, DDR, 64M x 4, 60 Pin, Plastic, BGA |

| HYB18T256800AF-5 | 制造商:Infineon Technologies AG 功能描述: |

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

| HYB18T512400AF-5 | 制造商:Intersil Corporation 功能描述:SDRAM, DDR, 128M x 4, 60 Pin, Plastic, BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。