- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385420 > HY57V283220(L)T(P)-7 (Hynix Semiconductor Inc.) 4 Banks x 1M x 32Bit Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HY57V283220(L)T(P)-7 |

| 廠商: | Hynix Semiconductor Inc. |

| 英文描述: | 4 Banks x 1M x 32Bit Synchronous DRAM |

| 中文描述: | 4銀行× 1米x 32Bit的同步DRAM |

| 文件頁(yè)數(shù): | 5/15頁(yè) |

| 文件大小: | 913K |

| 代理商: | HY57V283220(L)T(P)-7 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

Rev. 0.9 / July 2004

5

HY57V283220(L)T(P) / HY5V22(L)F(P)

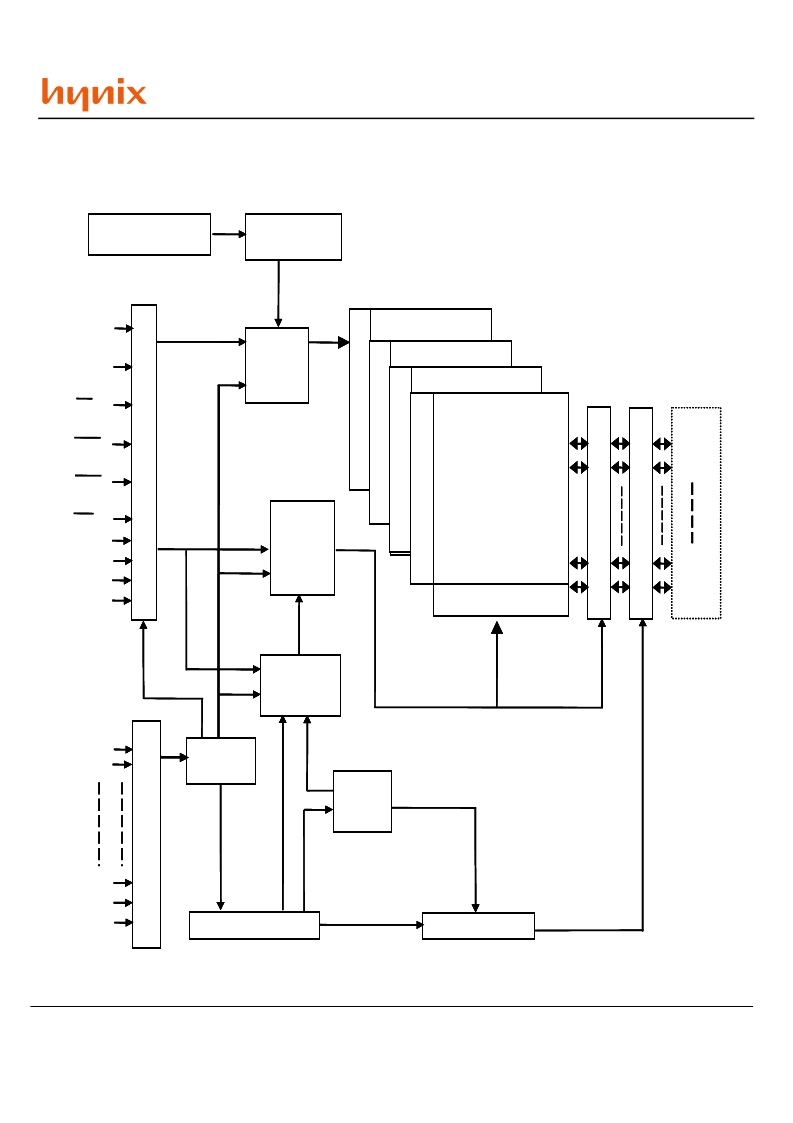

FUNCTIONAL BLOCK DIAGRAM

1Mbit x 4banks x 32 I/O Synchronous DRAM

A1

BA1

Register

Mode Register

Decoder

Decoder

Counter

Row Active

Active

Counter

Data Out Control

CAS Latency

Counter

DQ0

DQ1

DQ30

DQ31

& Timer

Pipe Line Control

Bank Select

CLK

CKE

CS

RAS

CAS

DQM3

x32 Bank 3

Array

Y decoder

1M x32 Bank 0

1M x32 Bank 1

1M x32 Bank 2

1M

X

S

A0

A11

BA0

A

Address

Row

Pre

Column

Pre

Column Add

Column

Burst

Refresh

Self Refresh Logic

I

S

WE

DQM0

DQM1

DQM2

X

X

Cell

Memory

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY57V283220(L)T(P)-8 | 4 Banks x 1M x 32Bit Synchronous DRAM |

| HY57V28820HCLT-6I | 4Banks x 4M x 8bits Synchronous DRAM |

| HY57V28820HCLT-8I | 4Banks x 4M x 8bits Synchronous DRAM |

| HY57V28820HCLT-HI | 4Banks x 4M x 8bits Synchronous DRAM |

| HY57V28820HCLT-KI | 4Banks x 4M x 8bits Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY57V283220LTP-7 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Banks x 1M x 32Bit Synchronous DRAM |

| HY57V283220LTP-8 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Banks x 1M x 32Bit Synchronous DRAM |

| HY57V283220LTP-H | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Banks x 1M x 32Bit Synchronous DRAM |

| HY57V283220LTP-P | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Banks x 1M x 32Bit Synchronous DRAM |

| HY57V283220LTP-S | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4 Banks x 1M x 32Bit Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。