- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385406 > HT9172 (Holtek Semiconductor Inc.) DTMF Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | HT9172 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | DTMF Receiver |

| 中文描述: | 雙音多頻接收器 |

| 文件頁(yè)數(shù): | 2/13頁(yè) |

| 文件大小: | 124K |

| 代理商: | HT9172 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

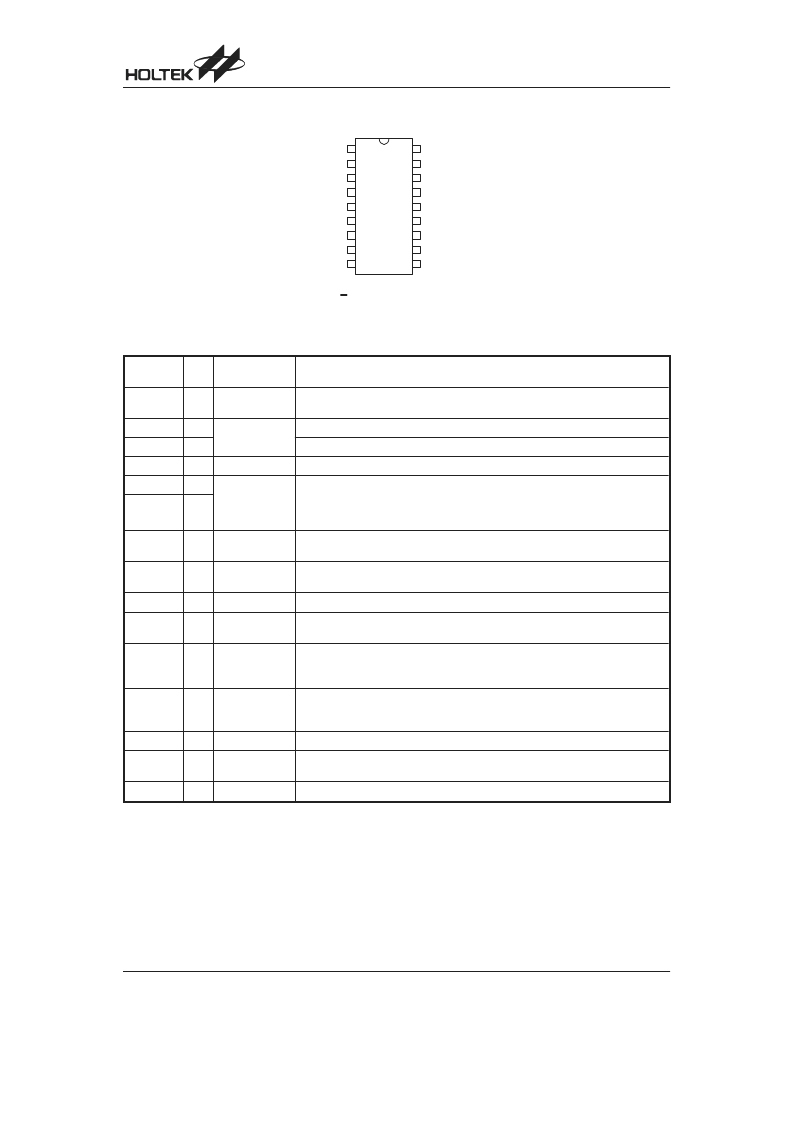

Pin Assignment

Pin Description

Pin Name

I/O

Internal

Connection

Description

VP

I

Operational

Amplifier

Operational amplifier non-inverting input

VN

I

Operational amplifier inverting input

GS

O

Operational amplifier output terminal

VREEF

O

VREF

Reference voltage output, normally V

DD

/2

X1

I

oscillator

The system oscillator consists of an inverter, a bias resistor and the required

on-chip load capacitor.

A standard 3.579545MHz crystal connected to the X1 and X2 terminals imple-

ments the oscillator function.

X2

O

PWDN

I

CMOS IN

Pull-low

Active high. This enables the device to go into its power down mode and inhibits

the oscillator. This pin input is pulled low internally.

INH

I

CMOS IN

Pull-low

Active high. This inhibits the detection of tones representing characters A, B, C

and D. This pin input is pulled low internally.

VSS

Negative power supply, ground

OE

I

CMOS IN

Pull-high

D0~D3 output enable, active high

D0~D3

O

CMOS OUT

Tristate

Received data output terminals

OE= H : Output enable

OE= L : High impedance

DV

O

CMOS OUT

Data valid output.

When the device has received a valid DTMF tone, this line will go high; other-

wise it remains low.

EST

O

CMOS OUT

Early steering output - see Functional Description

RT/GT

I/O

CMOS IN/OUT

Tone acquisition time and release time can be set through connection with ex-

ternal resistor and capacitor.

VDD

Positive power supply, 2.5V~5.5V for normal operation

HT9172

Rev. 1.00

2

March 30, 2006

4

5

6

1

6

5

4

7

) )

. / 0

/

- % /

)

)

)

)

) 1

-

'

%

. - "

2 '

3

) '

% %

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT9200 | DTMF Generators |

| HT9200A | DTMF Generators |

| HT9200B | DTMF Generators |

| HT9202A | 1-Memory/2-Memory Tone/Pulse Dialer |

| HT9202B | 1-Memory/2-Memory Tone/Pulse Dialer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT9200 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:DTMF Generators |

| HT92000526-5 | 制造商:Rennsteig 功能描述:PACK CON III FEM |

| HT9200A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:DTMF Generators |

| HT9200A(8SOIC) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Tone Telephone Dialer |

| HT9200A_04 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:DTMF Generators |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。