- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385404 > HT82K96E (Holtek Semiconductor Inc.) 8-Bit USB Multimedia Keyboard Encoder OTP MCU PDF資料下載

參數(shù)資料

| 型號: | HT82K96E |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit USB Multimedia Keyboard Encoder OTP MCU |

| 中文描述: | 8位USB多媒體鍵盤編碼器檢察官辦公室單片機 |

| 文件頁數(shù): | 10/46頁 |

| 文件大小: | 325K |

| 代理商: | HT82K96E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

HT82K96E

Rev. 1.70

10

April 22, 2004

The TO flag can be affected only by system power-up, a

WDT time-out or executing the CLR WDT or HALT

instruction. The PDF flag can be affected only by ex-

ecuting the HALT or CLR WDT instruction or dur-

ing a system power-up.

The Z, OV, AC and C flags generally reflect the status of

the latest operations.

In addition, on entering the interrupt sequence or exe-

cuting the subroutine call, the status register will not be

pushed onto the stack automatically. If the contents of

the status are important and if the subroutine can cor-

rupt the status register, precautions must be taken to

save it properly.

Interrupt

The device provides an external interrupt and internal

timer/event counter interrupts. The Interrupt Control

Register (INTC;0BH) contains the interrupt control bits

tosettheenable/disableandtheinterruptrequestflags.

Once an interrupt subroutine is serviced, all the other in-

terrupts will be blocked (by clearing the EMI bit). This

schememaypreventanyfurtherinterruptnesting.Other

interrupt requests may occur during this interval but only

the interrupt request flag is recorded. If a certain inter-

rupt requires servicing within the service routine, the

EMI bit and the corresponding bit of the INTC may be set

to allow interrupt nesting. If the stack is full, the interrupt

request will not be acknowledged, even if the related in-

terruptisenabled,untiltheSPisdecremented.Ifimmedi-

ate service is desired, the stack must be prevented from

becoming full.

All these kinds of interrupts have a wake-up capability.

As an interrupt is serviced, a control transfer occurs by

pushing the program counter onto the stack, followed by

a branch to a subroutine at specified location in the pro-

gram memory. Only the program counter is pushed onto

the stack. If the contents of the register or status register

(STATUS) are altered by the interrupt service program

which corrupts the desired control sequence, the con-

tents should be saved in advance.

USB interrupts are triggered by the following USB

events and the related interrupt request flag (USBF; bit

4 of INTC) will be set.

The access of the corresponding USB FIFO from PC

The USB suspend signal from PC

The USB resume signal from PC

USB Reset signal

When the interrupt is enabled, the stack is not full and

the external interrupt is active, a subroutine call to loca-

tion 04H will occur. The interrupt request flag (USBF)

and EMI bits will be cleared to disable other interrupts.

When PC Host access the FIFO of the HT82K96E, the

corresponding request bit of USR is set, and a USB in-

terrupt is triggered. So user can easy to decide which

FIFO is accessed. When the interrupt has been served,

the corresponding bit should be cleared by firmware.

When HT82K96E receive a USB Suspend signal from

Host PC, the suspend line (bit0 of USC) of the

HT82K96E is set and a USB interrupt is also triggered.

Also when HT82K96E receive a Resume signal from

Host PC, the resume line (bit3 of USC) of HT82K96E is

set and a USB interrupt is triggered.

Whatever there are USB reset signal is detected, the

USB interrupt is triggered.

The internal Timer/Event Counter 0 interrupt is initial-

ized by setting the Timer/Event Counter 0 interrupt re-

quest flag (; bit 5 of INTC), caused by a timer 0 overflow.

When the interrupt is enabled, the stack is not full and

the T0F bit is set, a subroutine call to location 08H will

occur. The related interrupt request flag (T0F) will be re-

setandtheEMIbitclearedtodisablefurtherinterrupts.

The internal timer/even counter 1 interrupt is initialized

by setting the Timer/Event Counter 1 interrupt request

flag (;bit 6 of INTC), caused by a timer 1 overflow. When

the interrupt is enabled, the stack is not full and the T1F

is set, a subroutine call to location 0CH will occur. The

related interrupt request flag (T1F) will be reset and the

EMI bit cleared to disable further interrupts.

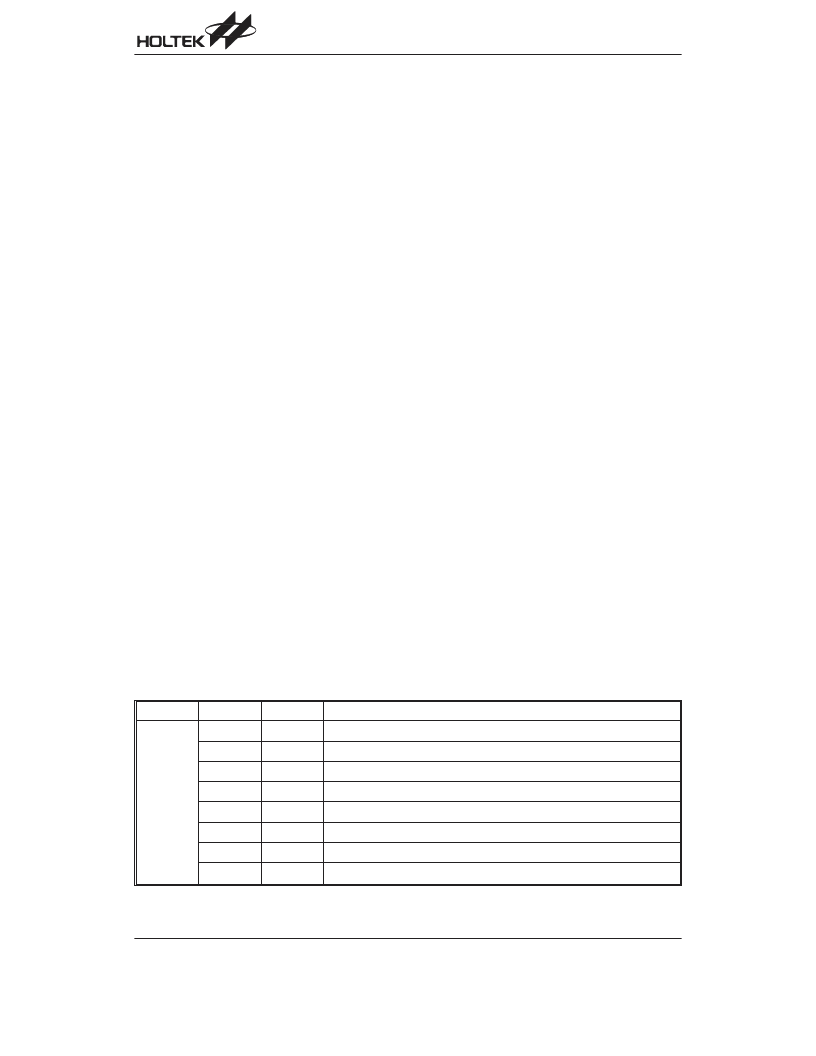

Register

Bit No.

Label

Function

INTC

(0BH)

0

EMI

Controls the master (global) interrupt (1= enabled; 0= disabled)

1

EUI

Controls the USB interrupt (1= enabled; 0= disabled)

2

ET0I

Controls the Timer/Event Counter 0 interrupt (1= enabled; 0= disabled)

3

ET1I

Controls the Timer/Event Counter 1 interrupt (1= enabled; 0= disabled)

4

USBF

USB interrupt request flag (1= active; 0= inactive)

5

T0F

Internal Timer/Event Counter 0 request flag (1= active; 0= inactive)

6

T1F

Internal Timer/Event Counter 1 request flag (1= active; 0= inactive)

7

Unused bit, read as 0

INTC Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82M21A | 3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22 | 5-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22A | 5-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M23C | 3/5-Key USB+PS/2 Optical Mouse Controller |

| HT82M23A | 3/5-Key USB+PS/2 Optical Mouse Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82K96E_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Multimedia Keyboard Encoder 8-Bit OTP MCU |

| HT82M13 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Mouse/Trackball Controller |

| HT82M21A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M21A_05 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:5-Key 3D USB+PS/2 Optical Mouse Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。